Top Level Design

- OBJECTIVE: Learn How to Develop A Top Level Design

- OBJECTIVE: Learn Key Information Necessary For Top Level Design

- OBJECTIVE: Learn How to Document Top Level Design

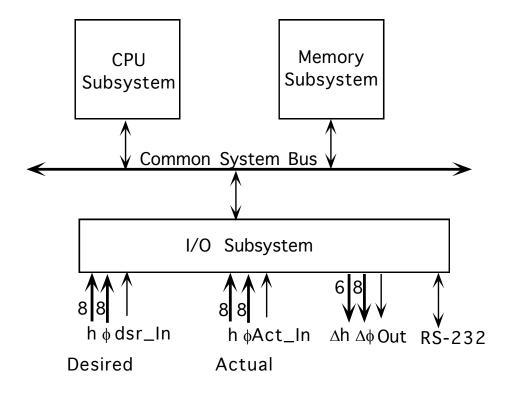

Top Level Design Block Diagram

- The Main Purpose of the Top Level Design Is the Where

- Make a List of the What and Find a Home For Each Requirement.

- » Can Use a Matrix

- » Modularize As Much As Possible. We Will Define Functional Subsystems

- Define Interface Between the Subsystems

- After The Subsystems and Interfaces are Defined, We Will Develop The Derived Requirements.

- » Assign Portions of Time Line, Size, Power etc to Each Subsystem

Make a List of the What and Find a Home For Each Requirement

Interfaces to Outside World {Parallel and Serial Ports} We will Create an <u>I/O Subsystem</u> Module for Interfaces

CPU

We Will Create A CPU Subsystem (Brains of System)

Memory

We Will Create a Memory Subsystem Module

Programs

Make Sure The Programs Are Accounted For Memory Map and Allocations (Enough Memory For Programs, Data)

# Subsystems on Common Bus Organization

# Requirements/Subsystem Matrix

#### Requirements Matrix Maps Requirements Into Appropriate System

|                    | CPU Subsystem       | Memory Subsystem | I/O Subsystem        |

|--------------------|---------------------|------------------|----------------------|

| Requirement        |                     |                  |                      |

| Current Position   |                     |                  | 2 8-bit Par. Inputs  |

| Desired Position   |                     |                  | 2 8-bit Par. Inputs  |

| Output Deltas      |                     |                  | 6,8-bit Par. Outputs |

| Arithmetic Ops     | 2's comp. Integer   |                  |                      |

| Data Requirement   |                     | 2kbyte Min RAM   |                      |

| Data Size          | 8 bit               | 8 bit            | 8 bit                |

| Program            |                     | 4kbyte Min ROM   |                      |

| Debug Data         |                     | 2kbyte Min RAM   |                      |

| Debug Prog         |                     | 4kbyte ROM       |                      |

| Debug Input/Output |                     |                  | RS232                |

| FunctionalUpdate   | 2,000 Instrs/Update |                  |                      |

|                    |                     |                  |                      |

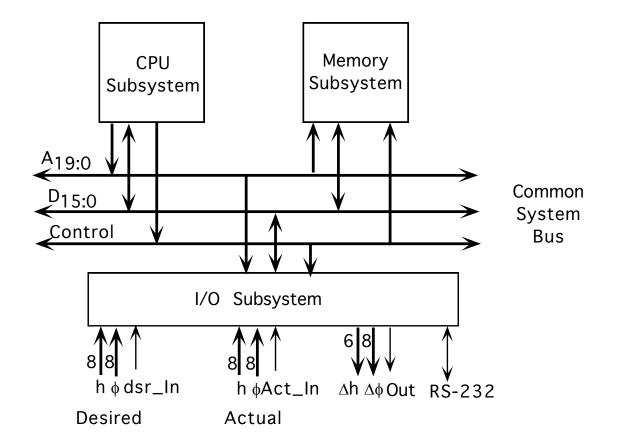

# **Common Bus Organization**

- CPU Provides All Addressing And Must Be Able To Access All Addresses/Data In System

- Address Map Is A Must

- "Which Came First, Chicken or Egg ?"

- » How Do We Get Data In/Out?

- » What Does System Bus Look Like?

# **Common Bus Definition**

- The Bus Signals Are Generated From The CPU In Our System: We Must Know A Little About The CPU In Order To Define The Bus.

- Based On Requirements, The CPU Can Be Simple:

- » Data 8 Bit Signed

- » Addressing: < 1 Meg

- » Integer Arithmetic

- These Requirements Easily Achievable With Wide Variety Of CPU's.

- We Can Base Our Decision:

- » Prior Experience With CPU's (What You Are Familiar With)

- » Development/Support Environment

Lets Choose The Intel 8086

# Intel 8086 Signals

| <ul> <li>Three Functional Busses:</li> <li>Address</li> <li>A<sub>19</sub> - AD<sub>0</sub></li> <li>» Data</li> <li>AD<sub>15</sub> - AD<sub>0</sub></li> </ul>    |                                                          | 2<br>3<br>4 8086<br>5<br>6<br>7<br>8<br>9<br>10 | 40 V <sub>CC</sub><br>39 AD <sub>15</sub><br>38 A <sub>16</sub><br>37 A <sub>17</sub><br>36 A <sub>17</sub><br>36 A <sub>18</sub><br>34 A <sub>19</sub><br>33 BHE<br>32 MN/MX<br>31 RD<br>40 LD<br>40 LD<br>40 LD<br>40 LD<br>40 LD |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>» Control</li> <li>Group1 Data Xfer {ALE, RD, WR, BHE, M/IO}</li> <li>Group2 Interrupts {INTR,NMI,INTA}</li> <li>Group3 Bus Control {HOLD,HLDA}</li> </ul> | AD <sub>1</sub><br>AD <sub>0</sub><br>NMI<br>INTR<br>CLK | 14 7<br>15 7<br>16 7<br>17 7<br>18 7<br>19 7    | 28 M/IO<br>27 DT/R<br>26 DEN<br>25 ALE<br>24 INTA<br>23 TEST<br>22 READY<br>21 RESET                                                                                                                                                |

All Other Signals Will Stay Internal To CPU Subystem

# Common Bus

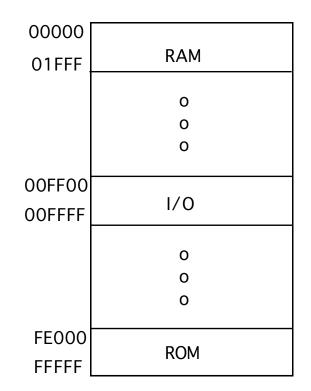

# Memory Map

- Purpose Of Memory Map Is To Show Design Teams Where They Should Decode Their Memory, Devices, Etc.

- Memory Must Be Large Enough To Hold:

- » RAM Input Data, Temp Data, All Structures, Stack, Heap, etc...

- » ROM Program, Initialization, Debug Monitor

- I/O Is Usually Memory Mapped (But Doesn't Need to Be)

- Provide A "Chunk" of Addresses (Assume Each Port Occupies an Address)

## **RAM Requirements**

- o Intel CPU's Want RAM Starting At Address x00000.

- We Need: Data Storage 2kbyte

Stack 2kbytes

Heap 2kbytes

Debug 2kbytes

8 kbytes

Lets Double16 kbytes (All 4kbytes Segs)

| 00000 | Data<br>4 kbytes  |

|-------|-------------------|

| 007FF |                   |

| 00800 | Debug<br>4 kbytes |

| 00FFF |                   |

| 01000 | Неар              |

| 017FF | 4 kbytes          |

| 01800 | 4 kbytes          |

| 01FFF | Stack             |

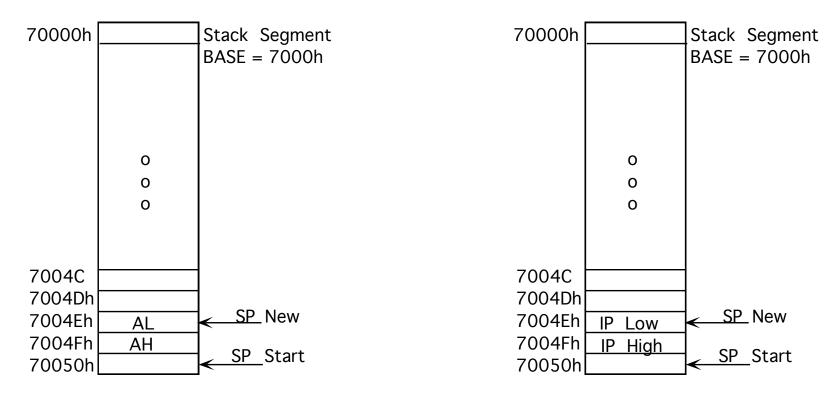

#### Stacks

- Stack: Temporary Storage Space: (Points to Last Valid Entry)

- » Pass Variables Between Subroutines Storage For Subroutine Calls

PUSH AX -near CALL

# Heaps

- Heap:

- » Memory Allocation During Run Time

- Int a[];

- Size Not Defined at Compile

- a = Malloc(100\*sizeof(int));

- » OS Usually Takes Care of This. We Will Write Our Own

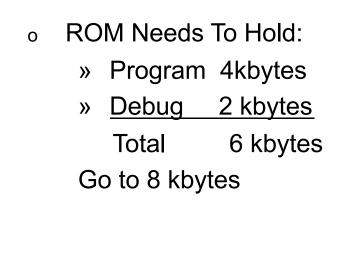

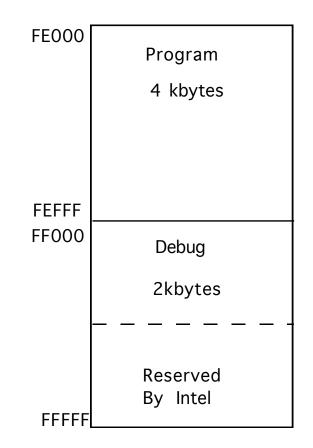

## **ROM Requirements**

## Address Map

Place Subsystems At Particular Address Block Range. This Guarantees That Parallel Design Teams Don't Overlap Address Decode.

# Top Level Design Summary

- o Create Subsystems

- » Modularize the System

- Requirements Matrix

- » Guarantee All Requirements Are Accounted For

- o Define Internal Interfaces

- » Define Signals/Data Structures Between Subsystems

- o Define Memory Map

- » Partitions System Address Space To Eliminate Overlap

Allows Multiple Groups To Work Simultaneously