## CSCE 4114 Uartlite

#### David Andrews

dandrews@uark.edu

1

computer System Design Lab

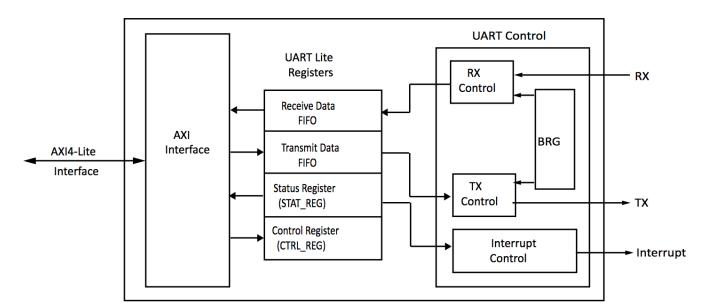

Soft IP version of a UART

16-character transmit and receive FIFO's

Configurable number of data bits (5-8)

Configurable Parity

Configurable Baud Rate

omputer System Design Lab

## Uartlite

Programmers View

| Base Address +<br>Offset (hex) | Register Name | Access<br>Type       | Default<br>Value (hex) | Description                |

|--------------------------------|---------------|----------------------|------------------------|----------------------------|

| C_BASEADDR + 0x0               | Rx FIFO       | Read (1)             | 0x0                    | Receive Data FIFO          |

| C_BASEADDR + 0x4               | Tx FIFO       | Write (2)            | 0x0                    | Transmit Data FIFO         |

| C_BASEADDR + 0x8               | STAT_REG      | Read (1)             | 0x4                    | UART Lite Status Register  |

| C_BASEADDR + 0xC               | CTRL_REG      | Write <sup>(2)</sup> | 0x0                    | UART Lite Control Register |

1. Writing of a read only register has no effect.

2. Reading of a write only register returns zero.

## Uartlite

- Transmit/Receive bytes

- Tx/Rx Channels are 16 Deep FIFO's.

Why ?

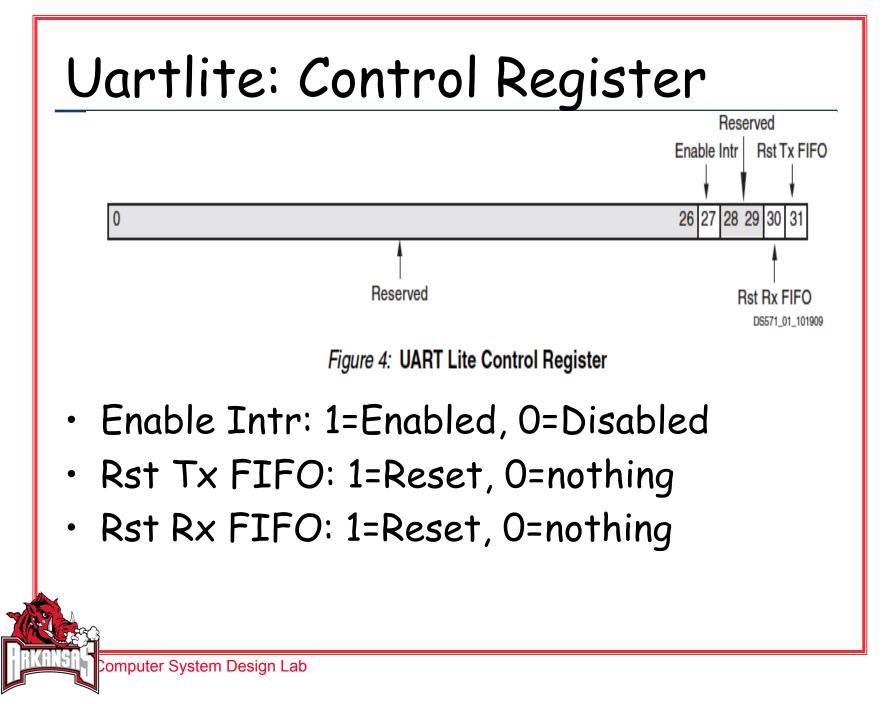

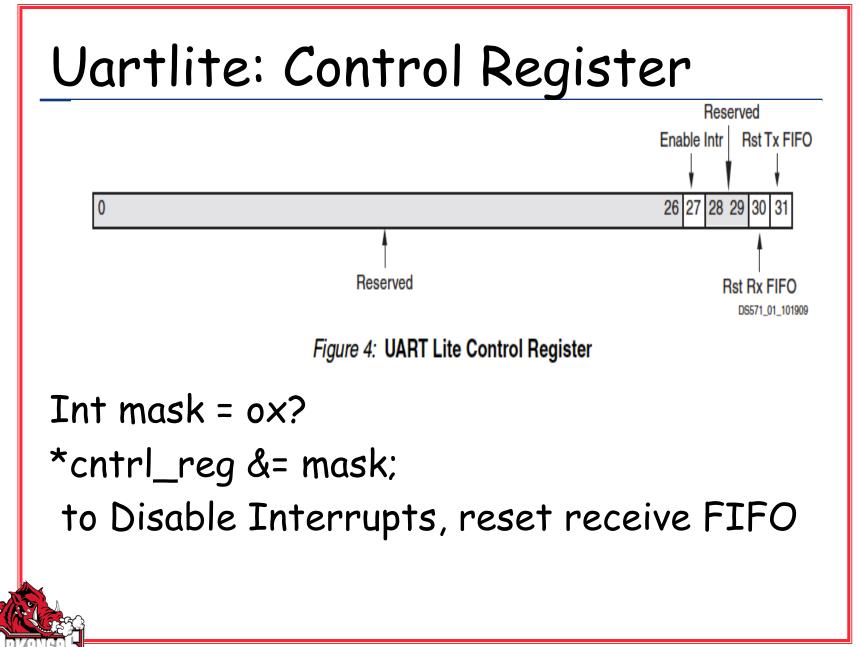

# some addresses/bit masks

Important memory offsets (in decimal):

UART\_RX\_FIFO offset is 0 (Used to read Rx\_FIFO values, read-only UART\_TX\_FIFO offset is 4 (Used to write Tx\_FIFO values, write only UART\_STATUS\_REG offset is 8 (Used to check UART status, read only) UART\_CONTROL\_REG offset is 12 (Used to configure UART, write-only)

## some addresses/bit masks

Important memory offsets (in decimal):

UART\_RX\_FIFO offset is 0 Used to read Rx\_FIFO values, read-only UART\_TX\_FIFO offset is 4 Used to write Tx\_FIFO values, write only UART\_STATUS\_REG offset is 8 Used to check UART status, read only UART\_CONTROL\_REG offset is 12 Used to configure UART, write-only

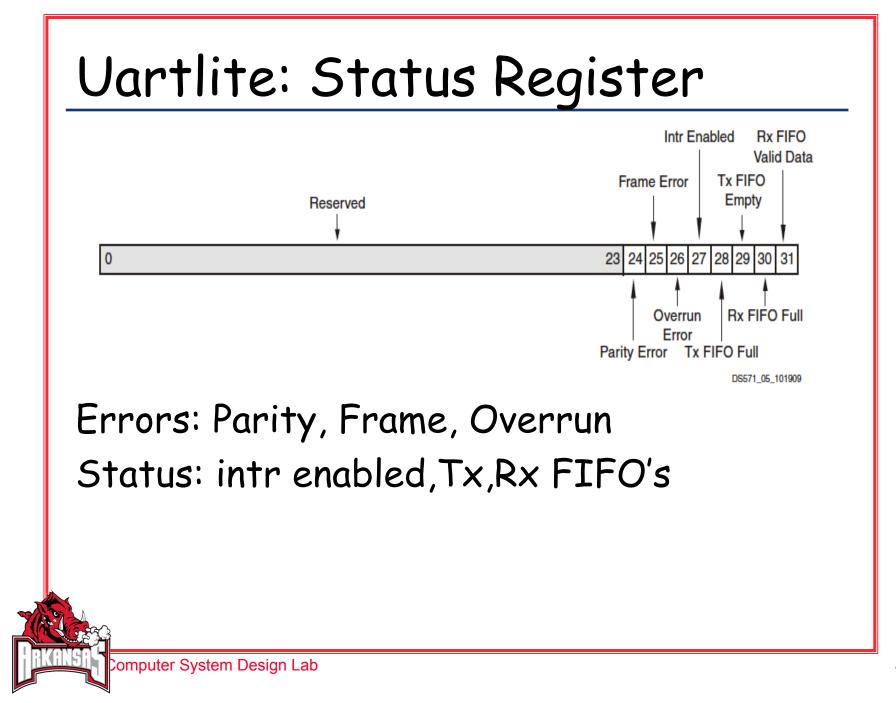

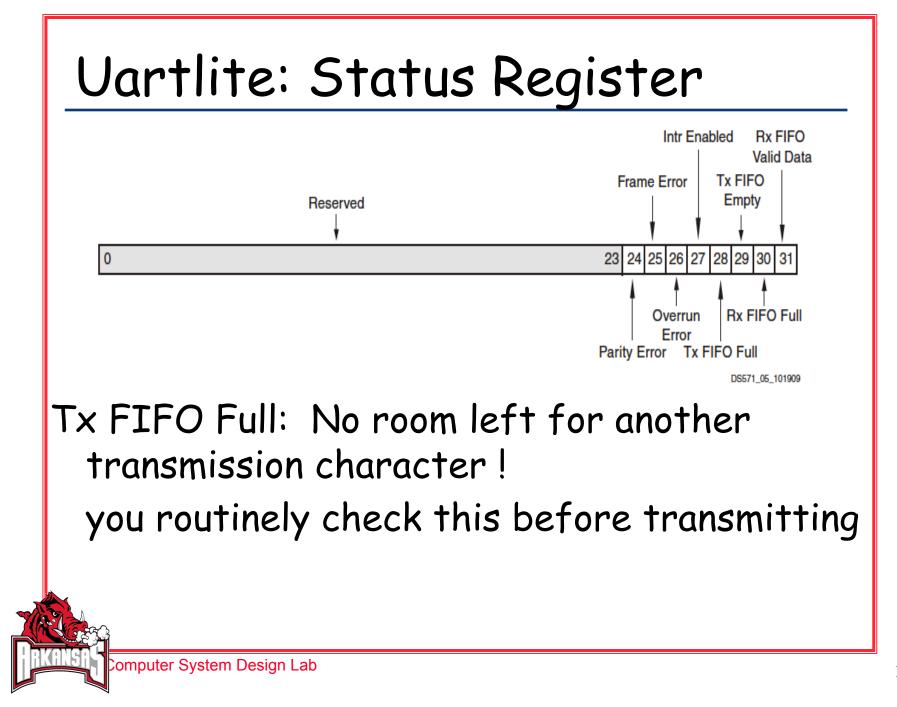

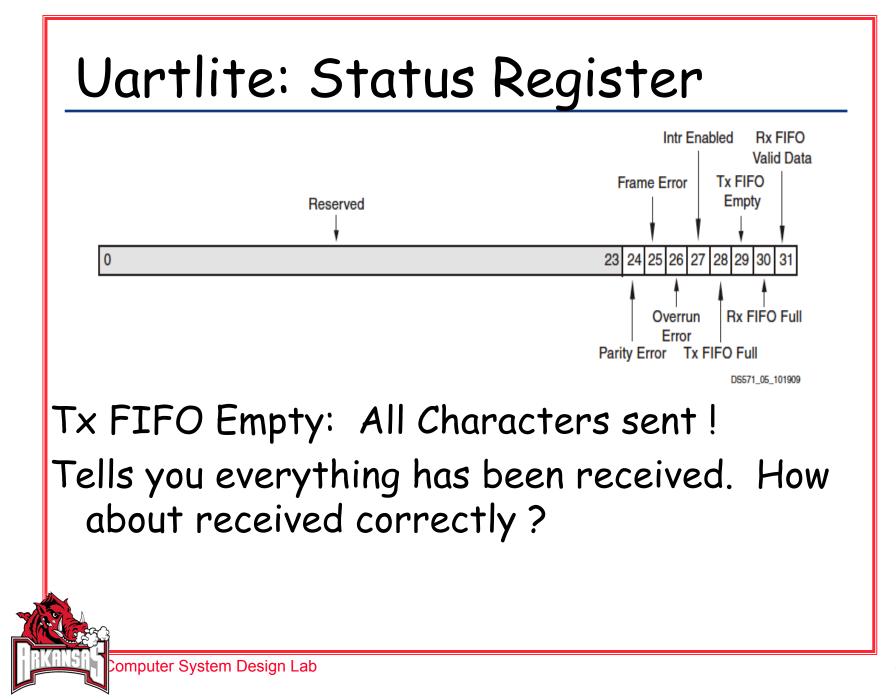

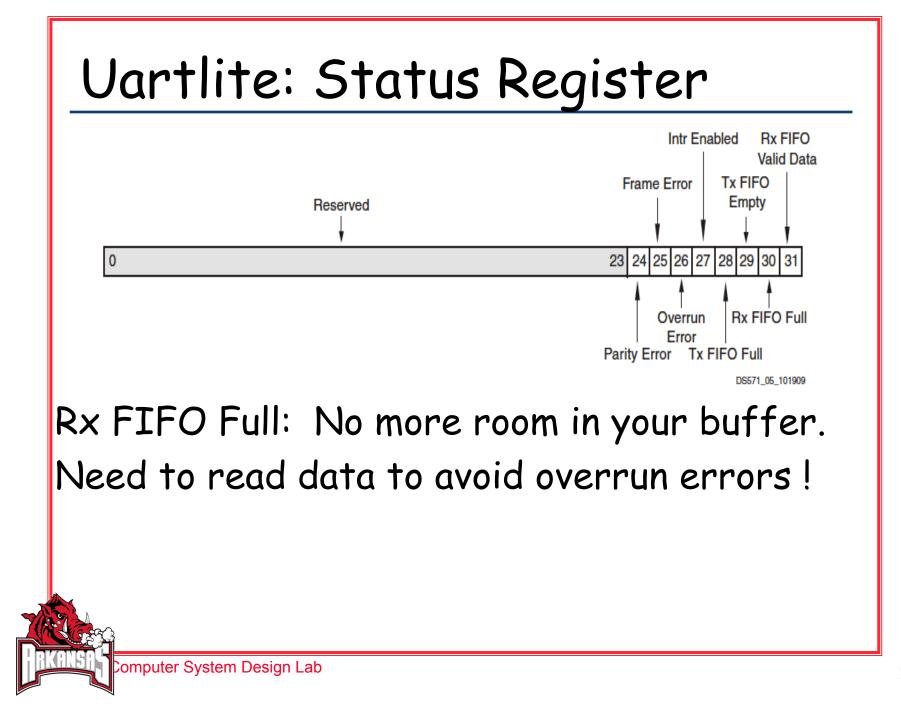

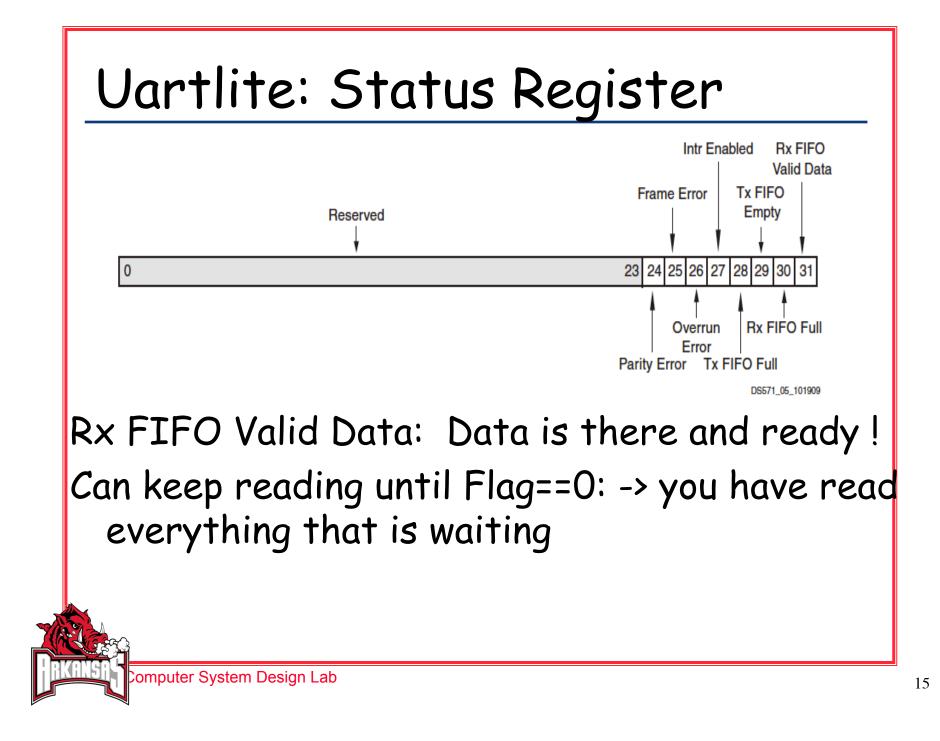

Important bit-masks (in decimal):

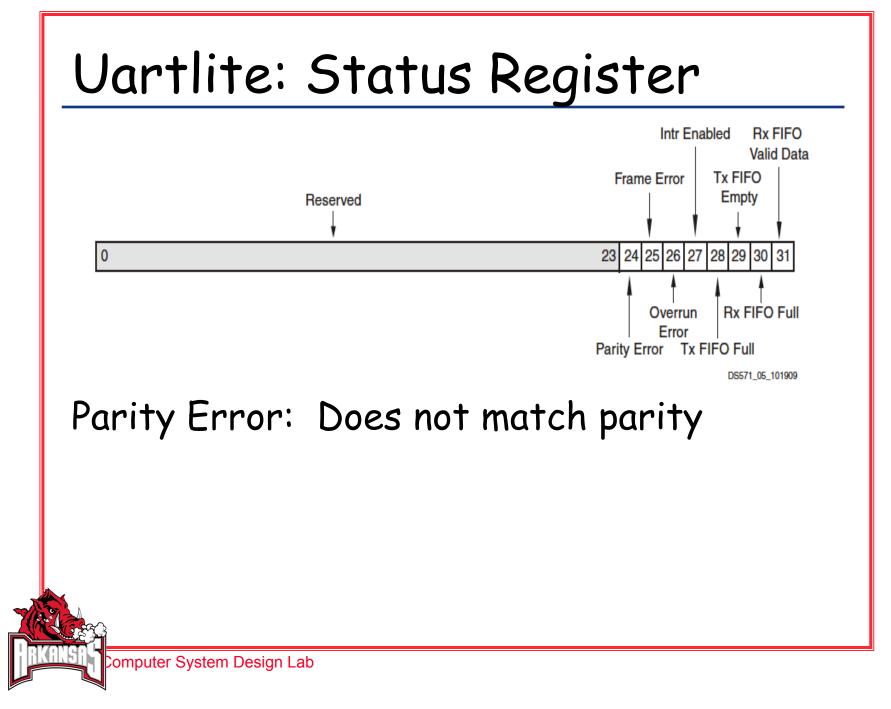

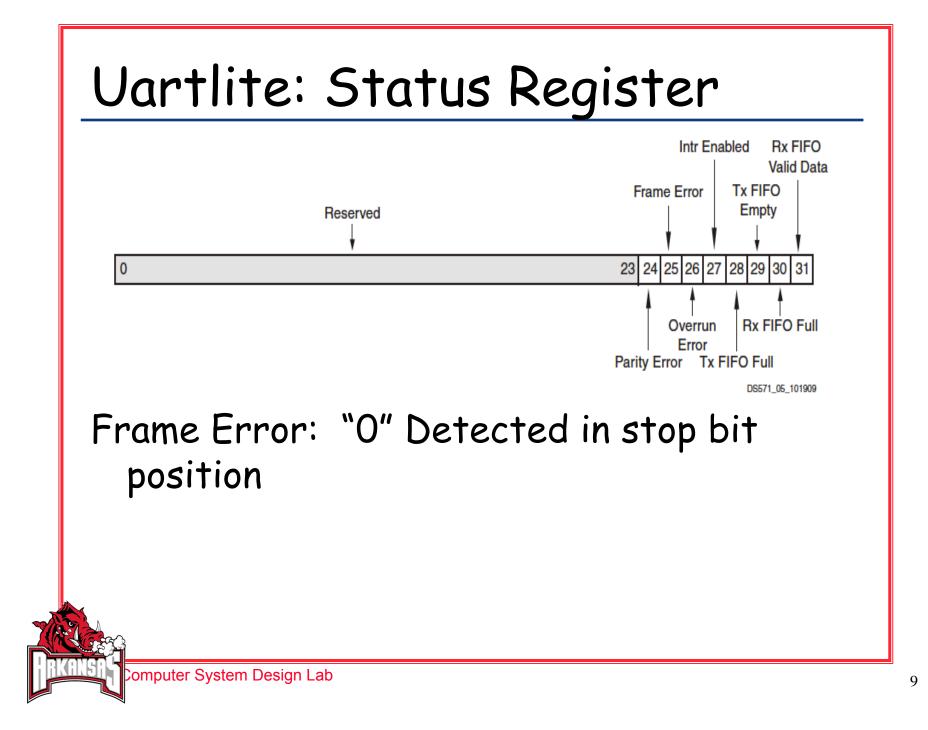

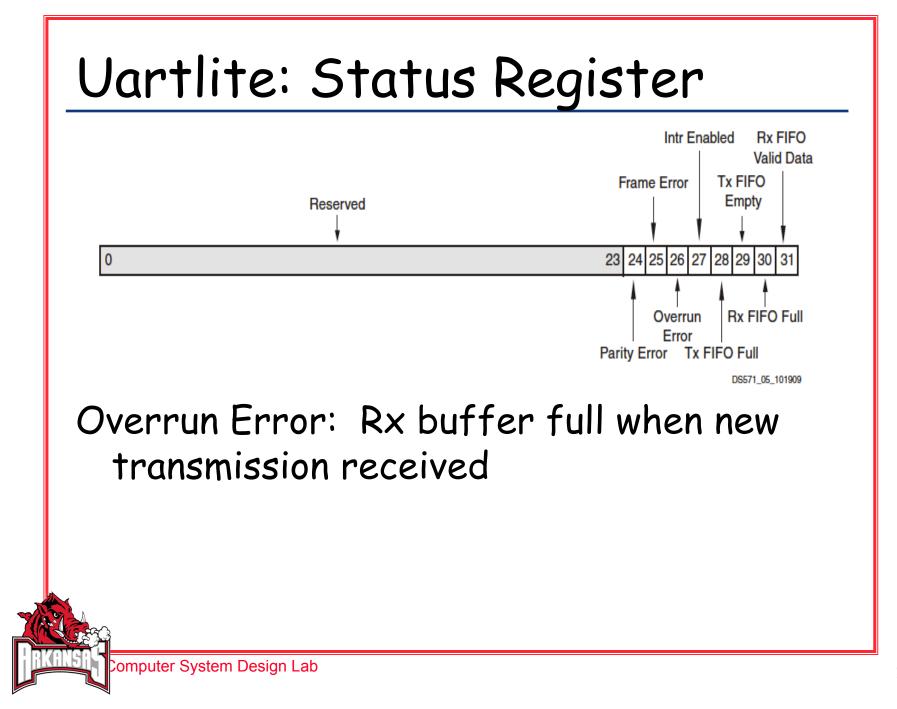

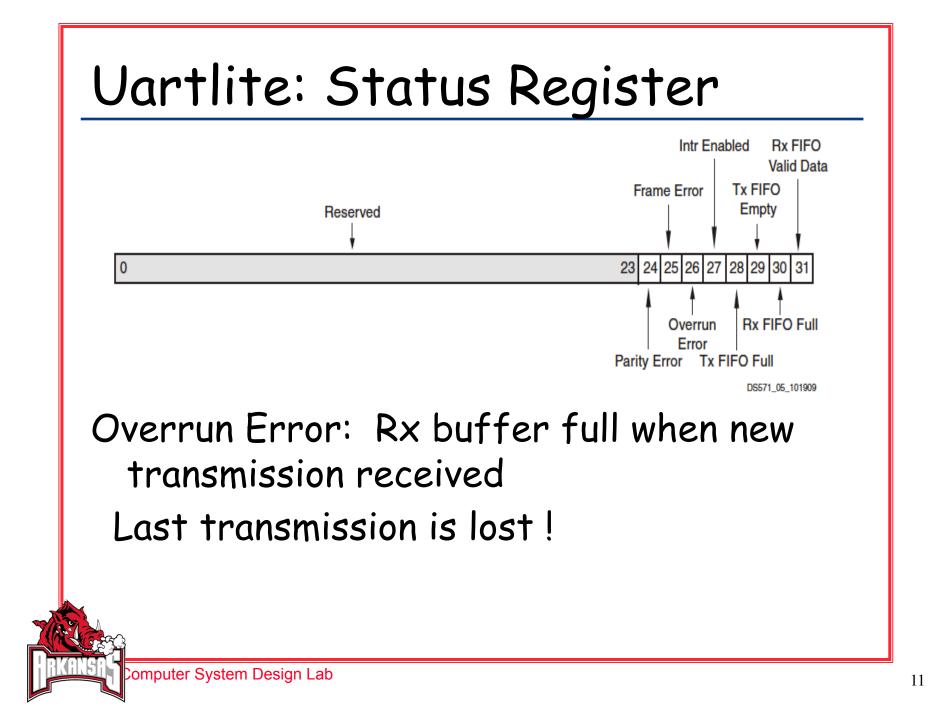

TX\_FIFO\_FULL 8 TX\_FIFO\_EMPTY 4 RX\_FIFO\_FULL 2 RX\_FIFO\_VALID 1 Used to check if the Tx\_FIFO is full Used to check if the Tx\_FIFO is empty Used to check if the Rx\_FIFO is full Used to check if the Rx\_FIFO has data

# How do I send information?

# Wait for Tx\_FIFO status to be NOT FULL Write character to Tx\_FIFO

# How do I send information?

# Wait for Tx\_FIFO status to be NOT FULL Write character to Tx\_FIFO

• You write the pseudo C code......

# How do I send information?

1) Wait for Tx\_FIFO status to be NOT FULL 2) Write character to Tx\_FIFO

• pseudo C code......

```

while (UART_STATUS == TX_FIFO_FULL) { };

TX_FIFO = my_char;

```

Assembler....

.set UART\_base, 1080033280 /\* 0x40600000 \*/

Assembler....

```

.set UART_base, 1080033280 /* 0x40600000 */

```

```

# Put UART's base address into r6

addik r6, r0, UART_base

```

```

Assembler....

```

```

.set UART_base, 1080033280 /* 0x40600000 */

```

```

# Put UART's base address into r6

addik r6, r0, UART_base

```

```

# Move character (byte) into r8 from character parameter (r5)

addik r8, r5, 0

```

#### 1) Wait for Tx\_FIFO status to be NOT FULL

#### 1) Wait for Tx\_FIFO status to be NOT FULL

.set TX\_FIFO\_FULL, 8 /\* Bit-mask for checking FIFO fullness \*/

#### 1) Wait for Tx\_FIFO status to be NOT FULL

.set TX\_FIFO\_FULL, 8 /\* Bit-mask for checking FIFO fullness \*/

# Wait until UART's TX FIFO is not full

myPrintCharLoop:

lwi r7, r6, UART\_STATUS\_REG\_OFFSET

#### 1) Wait for Tx\_FIFO status to be NOT FULL

.set TX\_FIFO\_FULL, 8 /\* Bit-mask for checking FIFO fullness \*/

# Wait until UART's TX FIFO is not full

myPrintCharLoop: lwi r7, r6, UART\_STATUS\_REG\_OFFSET

Base addr of uart already in r6

#### 1) Wait for Tx\_FIFO status to be NOT FULL

.set TX\_FIFO\_FULL, 8 /\* Bit-mask for checking FIFO fullness \*/

# Wait until UART's TX FIFO is not full

myPrintCharLoop:

lwi r7, r6, UART\_STATUS\_REG\_OFFSET

# Mask out the TX\_FIFO\_FLAG andi r7, r7, TX\_FIFO\_FULL

#### 1) Wait for Tx\_FIFO status to be NOT FULL

.set TX\_FIFO\_FULL, 8 /\* Bit-mask for checking FIFO fullness \*/

# Wait until UART's TX FIFO is not full

myPrintCharLoop:

lwi r7, r6, UART\_STATUS\_REG\_OFFSET

# Mask out the TX\_FIFO\_FLAG andi r7, r7, TX\_FIFO\_FULL

Checks only Tx\_FIFO\_Full Flag

#### 1) Wait for Tx\_FIFO status to be NOT FULL

.set TX\_FIFO\_FULL, 8 /\* Bit-mask for checking FIFO fullness \*/

# Wait until UART's TX FIFO is not full

myPrintCharLoop:

lwi r7, r6, UART\_STATUS\_REG\_OFFSET

# Loop back if it is not-zero bnei r7 myPrintCharLoop nop

#### 1) Wait for Tx\_FIFO status to be NOT FULL

.set TX\_FIFO\_FULL, 8 /\* Bit-mask for checking FIFO fullness \*/

# Wait until UART's TX FIFO is not full >myPrintCharLoop: lwi r7, r6, UART\_STATUS\_REG\_OFFSET

# Loop back if it is not-zero

bnei r7 myPrintCharLoop

nop

2) Send Character

.set UART\_TX\_FIFO\_OFFSET, 4 /\* transmit FIFO, write only \*,

```

2) Send Character

```

```

.set UART_TX_FIFO_OFFSET, 4 /* transmit FIFO, write only */

```

# Send character to the FIFO

swi r8, r6, UART\_TX\_FIFO\_OFFSET

# How do I receive?

- 1) Wait for Rx\_FIFO status to be VALID

- 2) Read a character from the Rx\_FIFO

Pseudo code......

# How do I receive?

Wait for Rx\_FIFO status to be VALID

Read a character from the Rx\_FIFO

Pseudo code......

while (UART\_STATUS !=RX\_FIFO\_VALID) { }; my\_char = RX\_FIFO;

#### 1) Wait for Rx\_FIFO status to be VALID

#### 1) Wait for Rx\_FIFO status to be VALID

# Put UART's base address into r6

addik r6, r0, UART\_base

# Wait until UART's RX FIFO is not empty

myGetCharLoop:

lwi r7, r6, UART\_STATUS\_REG\_OFFSET

#### 1) Wait for Rx\_FIFO status to be VALID

# Put UART's base address into r6

addik r6, r0, UART\_base

# Wait until UART's RX FIFO is not empty

myGetCharLoop:

lwi r7, r6, UART\_STATUS\_REG\_OFFSET

# Mask out the RX\_FIFO\_DATA\_VALID\_FLAG andi r7, r7, RX\_FIFO\_VALID

#### 1) Wait for Rx\_FIFO status to be VALID

# Put UART's base address into r6

addik r6, r0, UART\_base

# Wait until UART's RX FIFO is not empty

myGetCharLoop:

lwi r7, r6, UART\_STATUS\_REG\_OFFSET

# Mask out the RX\_FIFO\_DATA\_VALID\_FLAG andi r7, r7, RX\_FIFO\_VALID

# Loop back if it is zero beqi r7 myGetCharLoop nop

2) Get Character

2) Get Character

# Loop is over

#### # Get character from the RX-FIFO lwi r5, r6, UART\_RX\_FIFO\_OFFSET