- Most Embedded Systems have multiple timers used for different things.

- Operating Systems Scheduling

- Periodic Scheduling: When timer interrupt goes off, the scheduler is invoked to check for new decision.

What is this periodic timer called in Linux ?

- "One-Shot": Operating system sets a new point in time for evaluating the scheduling decision.

- Periodic scheduling is the norm in non-real time (or embedded systems) but not in real-time systems. Why ?

- Operating Systems Monitoring: Suppose a character is sent to the keyboard or across network and the system waits on a response.

- What happens if the keyboard or network hangs?

- "Watchdog Timer": A drop dead time that if no response is received, the timer generates an interrupt to kick OS into error processing.

- If all is well, when response is received, OS "cancels" the watchdog timer by resetting

- Operating System:

- Performance meters. OS uses timers to measure performance, system evaluation, tuning.

- DRAM refresh. Must periodically read all DRAM memory locations and re-write to maintain data.

- And of course.....keeping time of day.....

- Applications use timers for co-ordinating activities such as timed input/outputs.

- After detecting a car coming to an intersection, turn the pedestrian signal red and wait 20 seconds, then turn pedestrian signal green.

- Controlling a diamond cutter: Once cut is started, continue cutting for 15 msec's then stop !

# Hw/Sw Timers

- Systems contain multiple, but not great numbers of hardware timers.

- Multiple "software" timers can be provided that use a single hardware timer.

- -Multiple "one-shot" requests can be maintained as a linked list. Software sorts requests into time ordering and programs the hardware timer accordingly

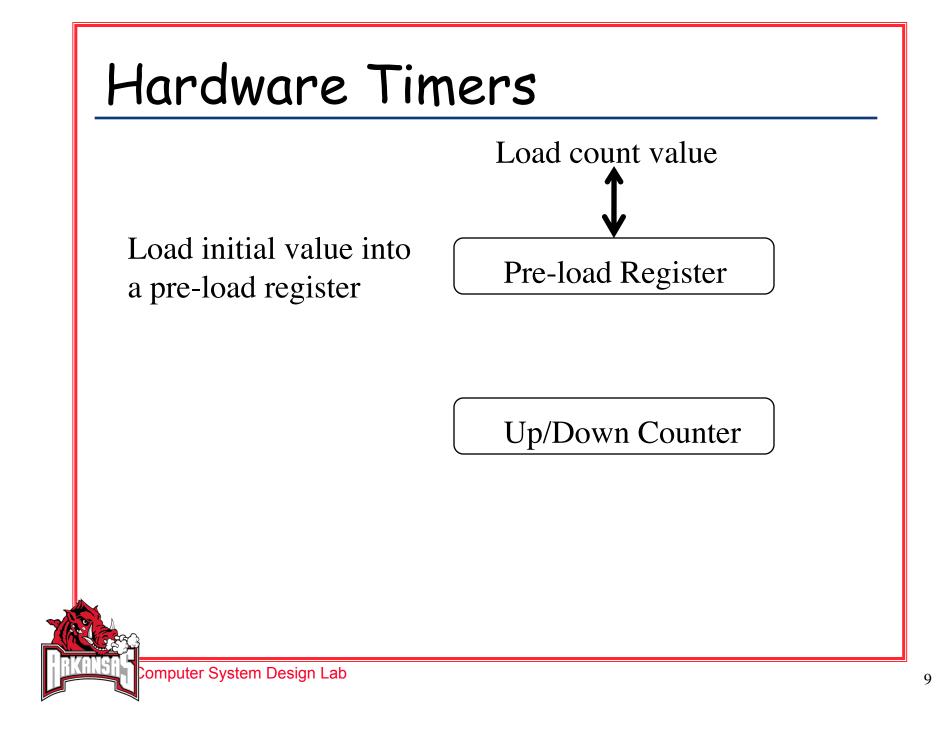

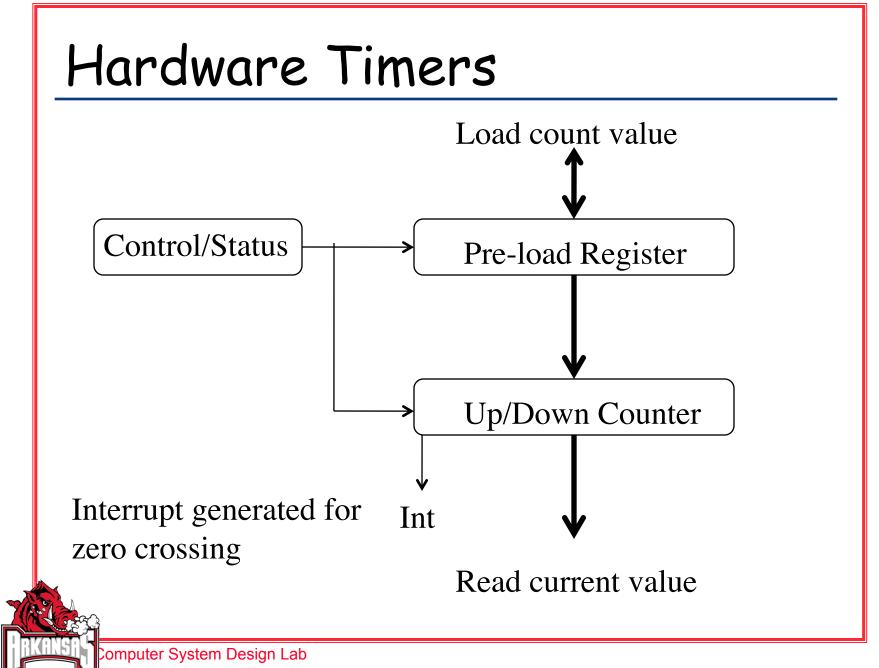

| Н | lardware Timers                      |

|---|--------------------------------------|

|   |                                      |

|   | Control/Status                       |

|   | Control: bits to allow configuration |

|   |                                      |

|   |                                      |

|   |                                      |

|   | Computer System Design Lab           |

| lard | ware |  | imers |  |

|------|------|--|-------|--|

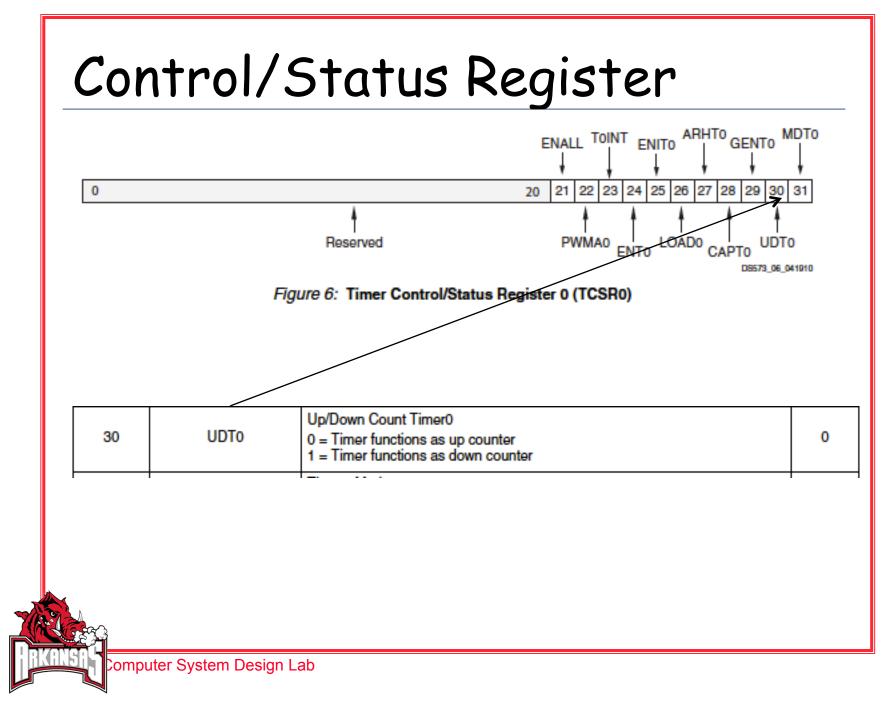

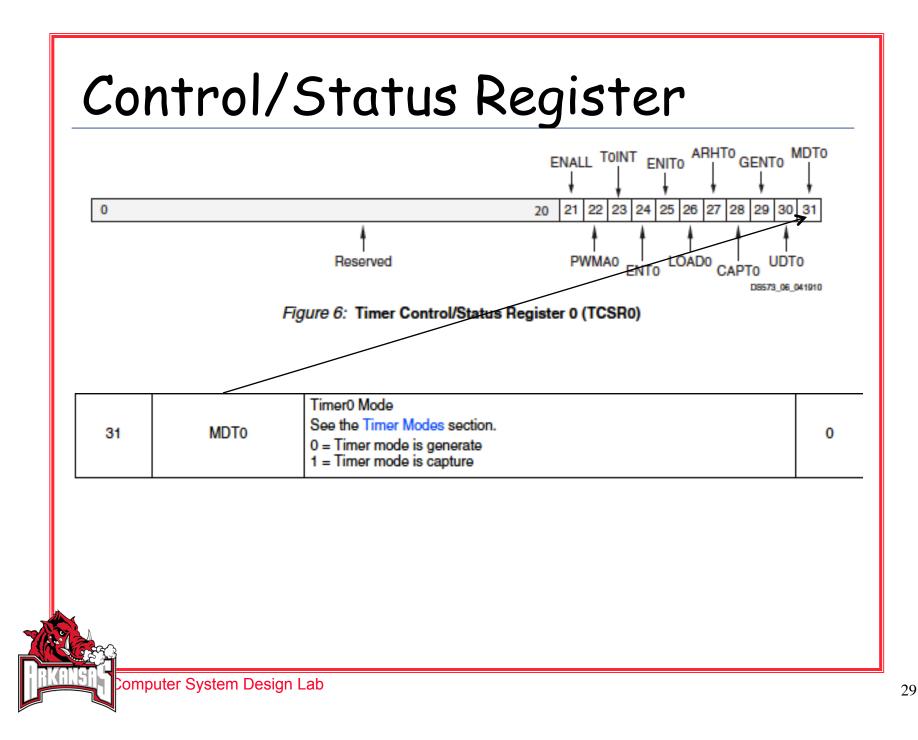

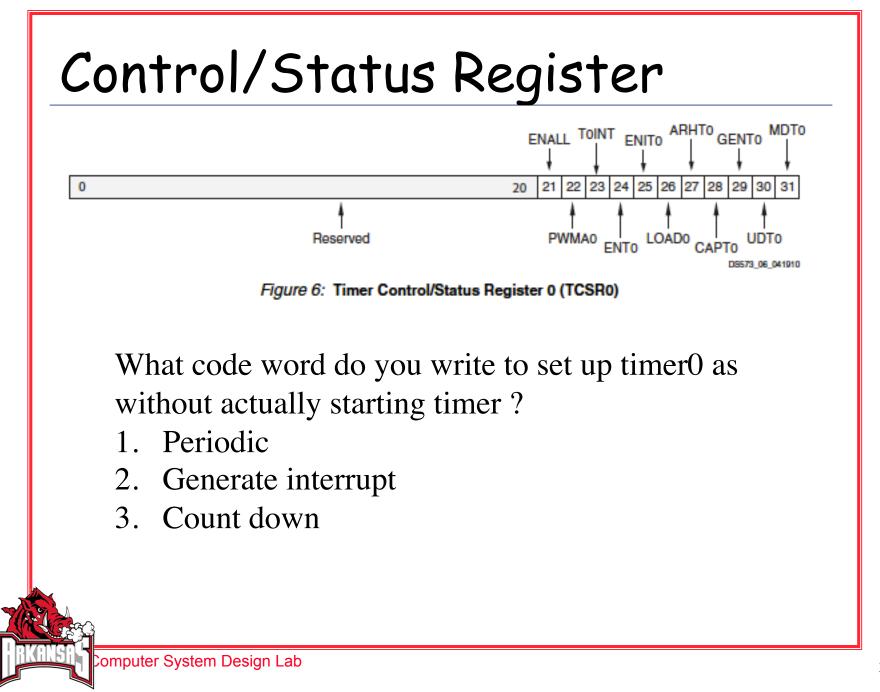

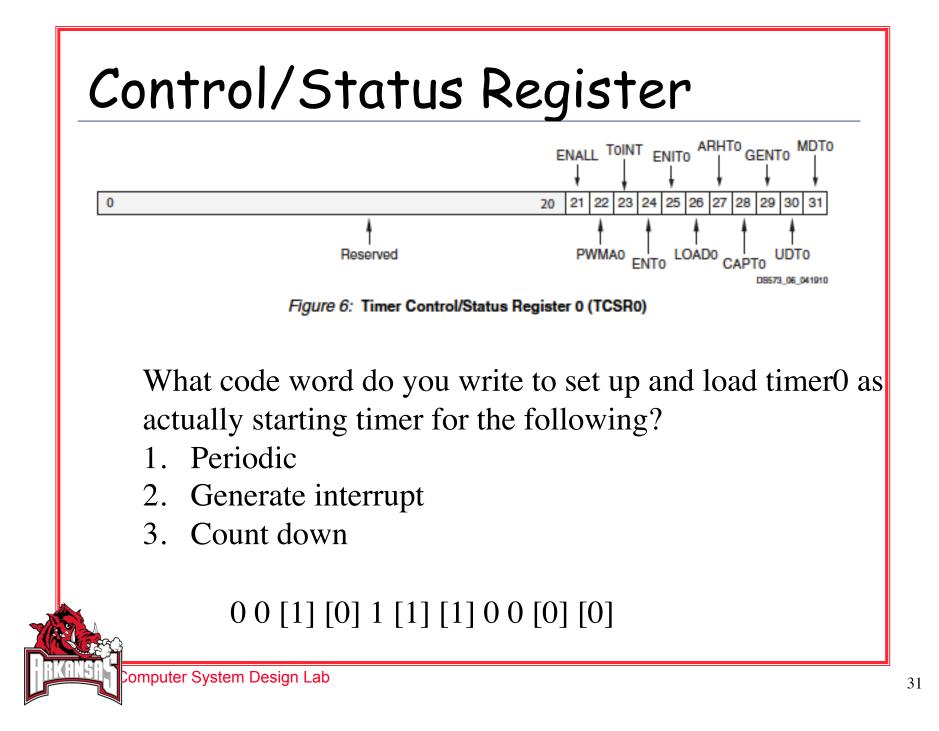

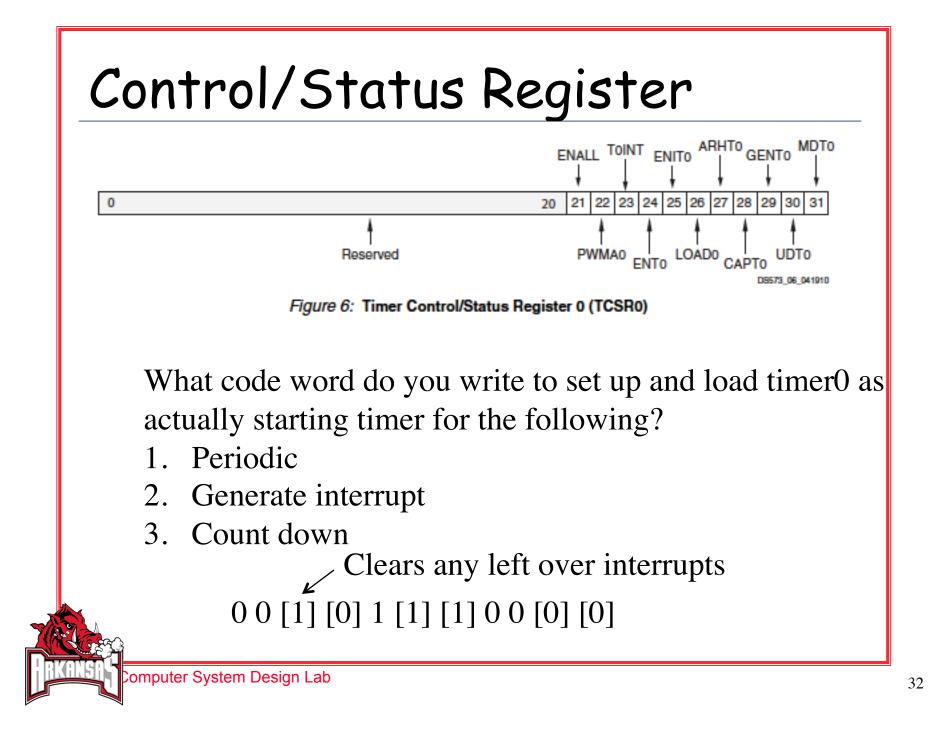

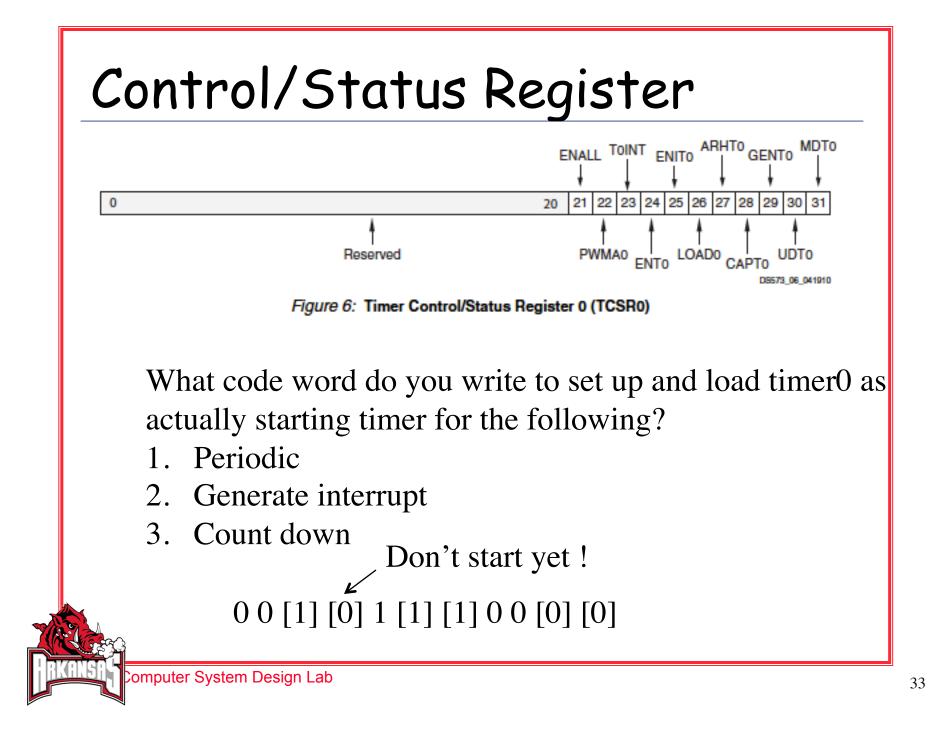

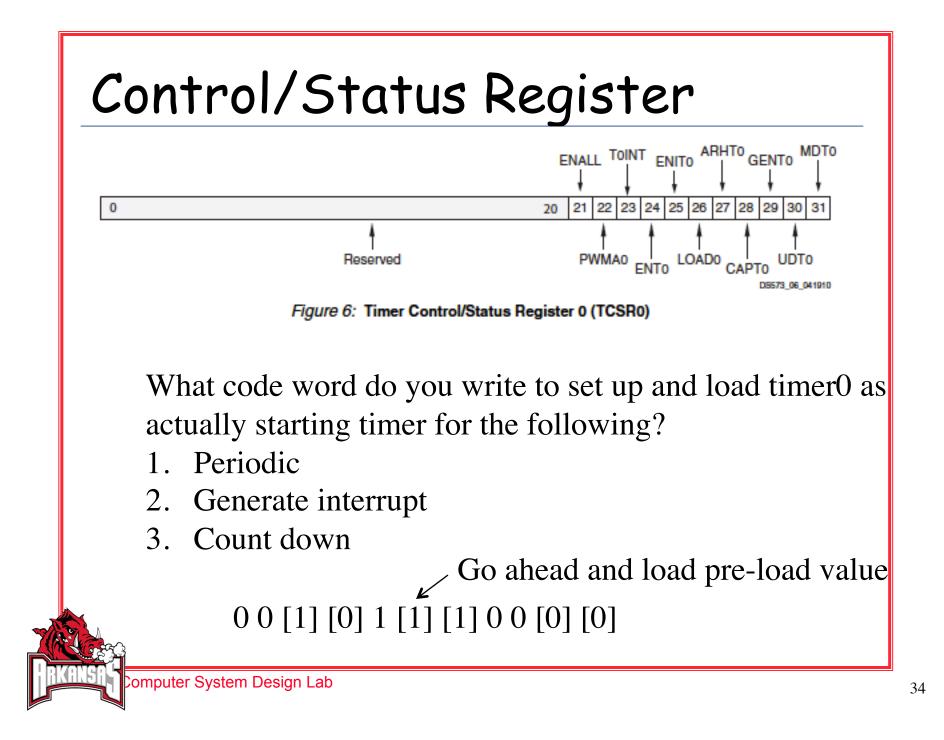

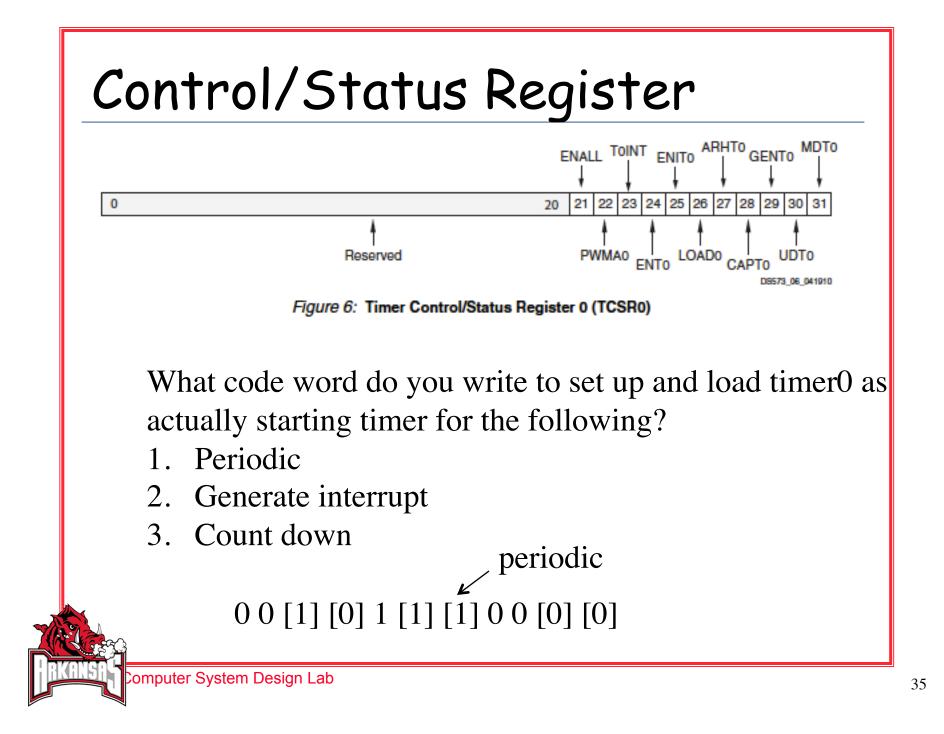

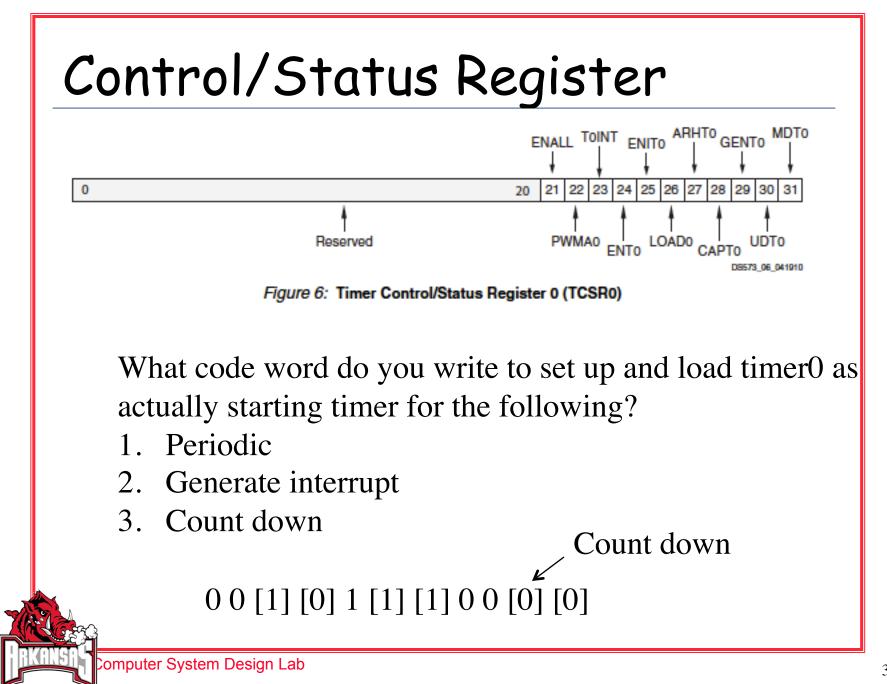

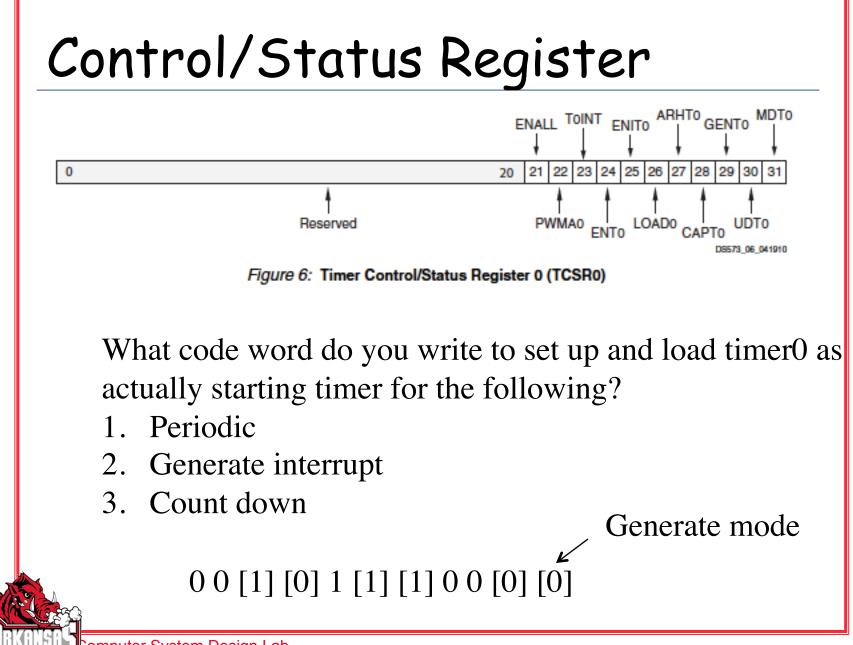

Control/Status

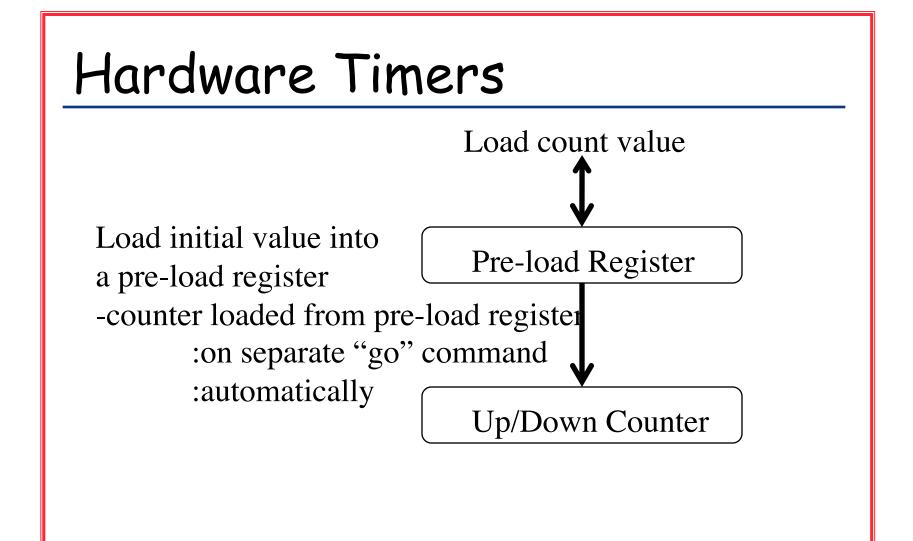

Control: bits to allow configuration -periodic: on zero crossing counter automatically loaded from pre-load immediately

## Hardware Timers

Control/Status

Control: bits to allow configuration -periodic: on zero crossing counter automatically loaded from pre-load immediately -one-shot: on zero crossing, counter not automatically loaded -start/stop: self explanatory

## Hardware Timers

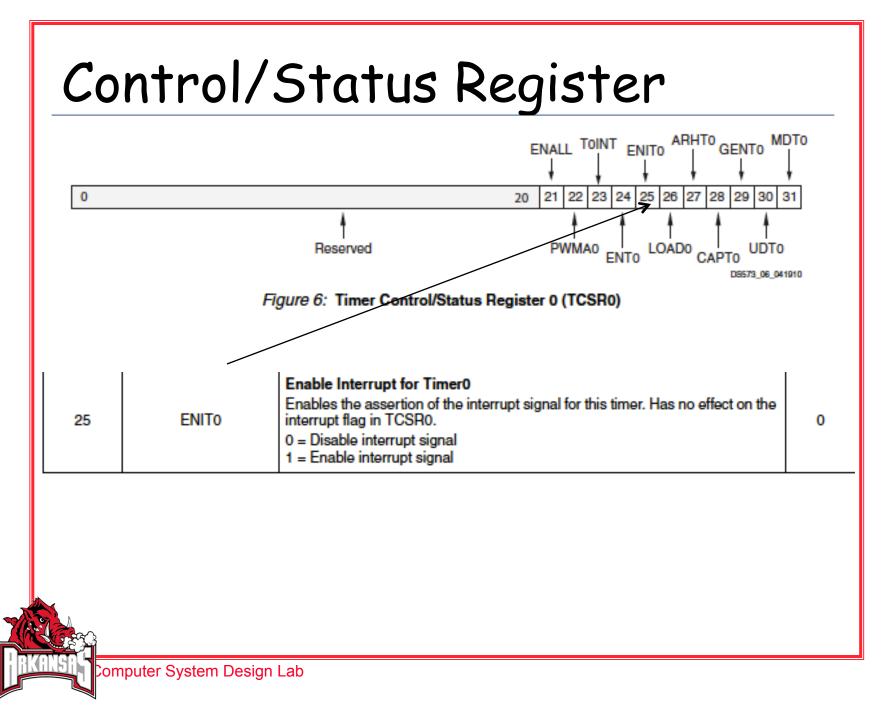

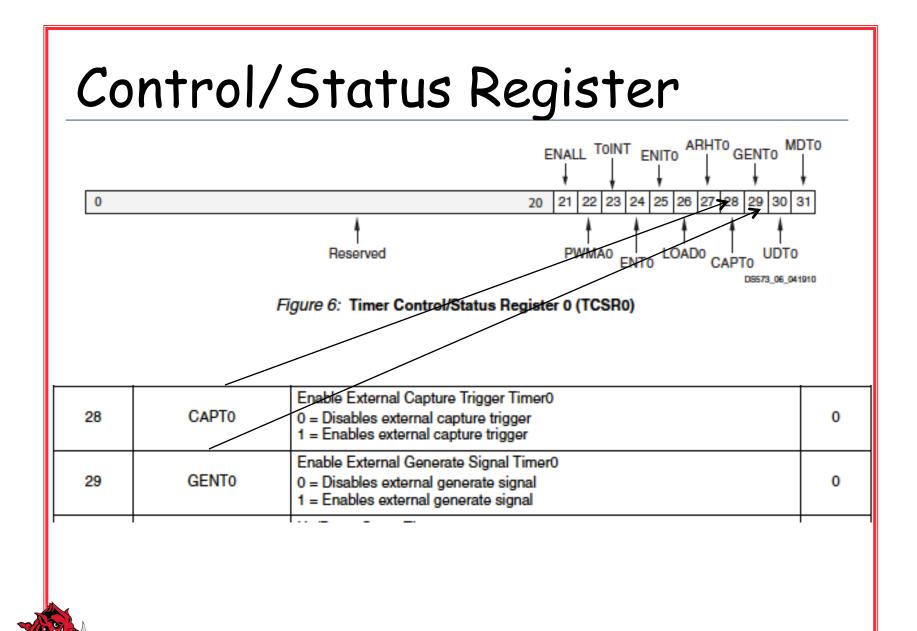

Control/Status

Control: bits to allow configuration -periodic: on zero crossing counter automatically loaded from pre-load immediately -one-shot: on zero crossing, counter not automatically loaded -start/stop: self explanatory -interrupt Enable/Disable: self explanatory

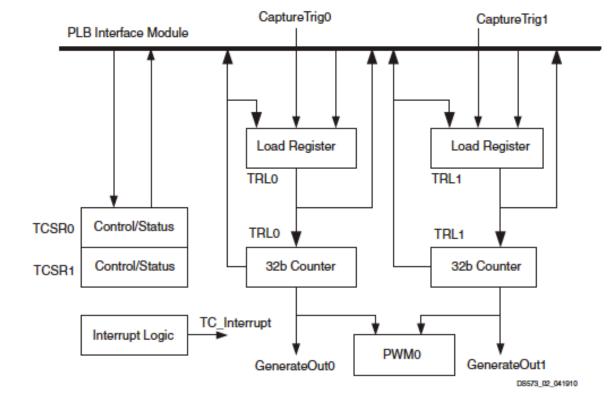

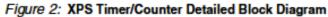

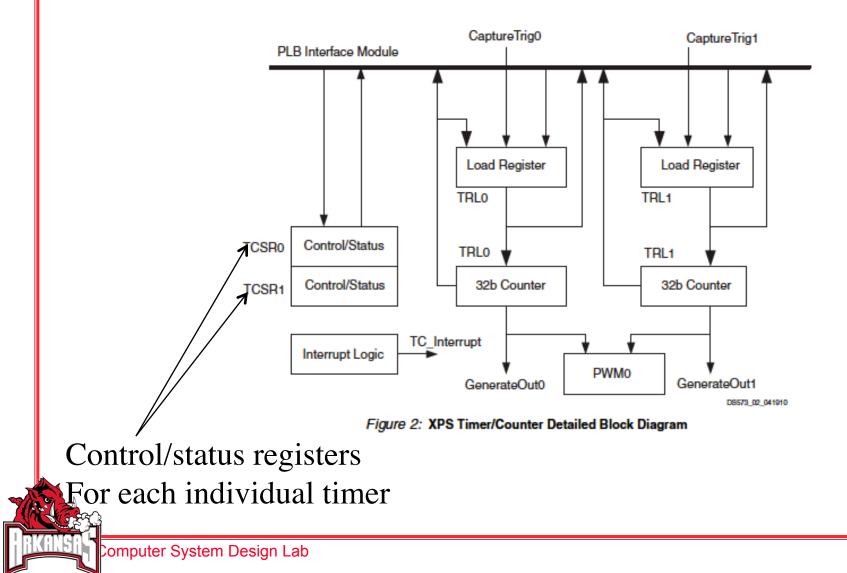

## Each Timer has 3 Modes

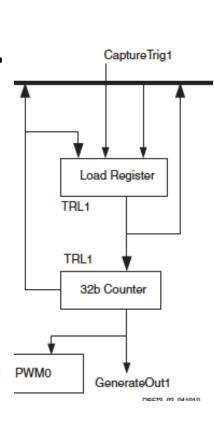

- Generate Mode

- Capture Mode

- Pulse Width Modulation

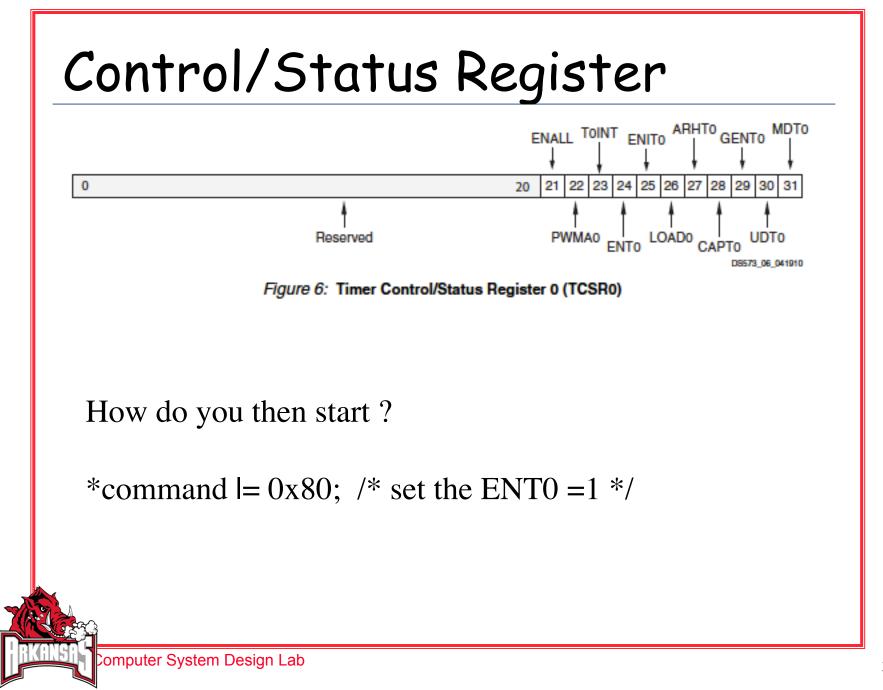

## Generate Mode

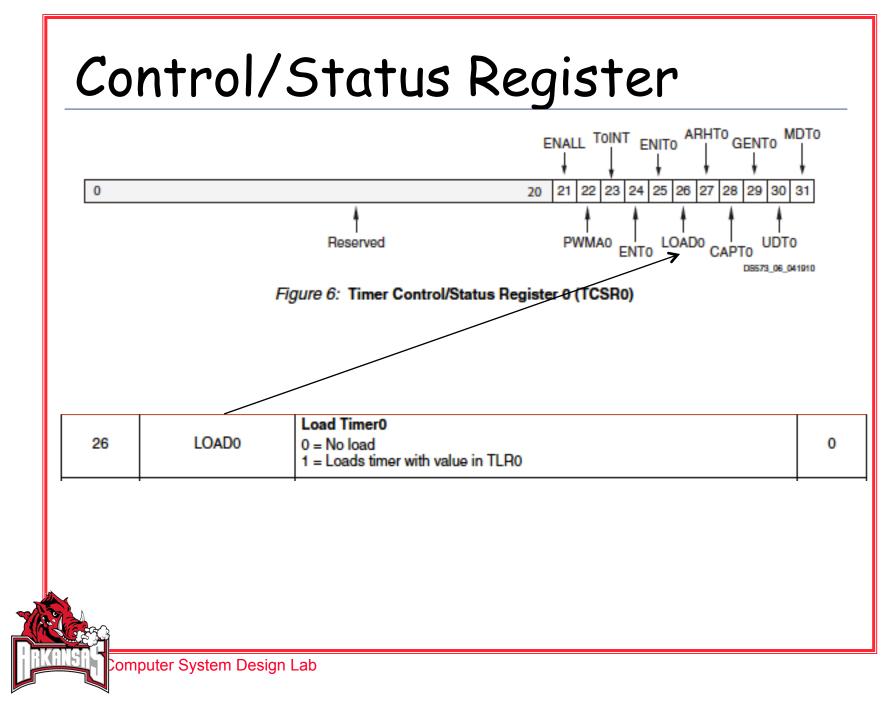

- Load register -> counter (load\_bit=1)

- Note\* Must be cleared before counter is enabled

- Set counter up or down (UDT bit)

- Start Counter

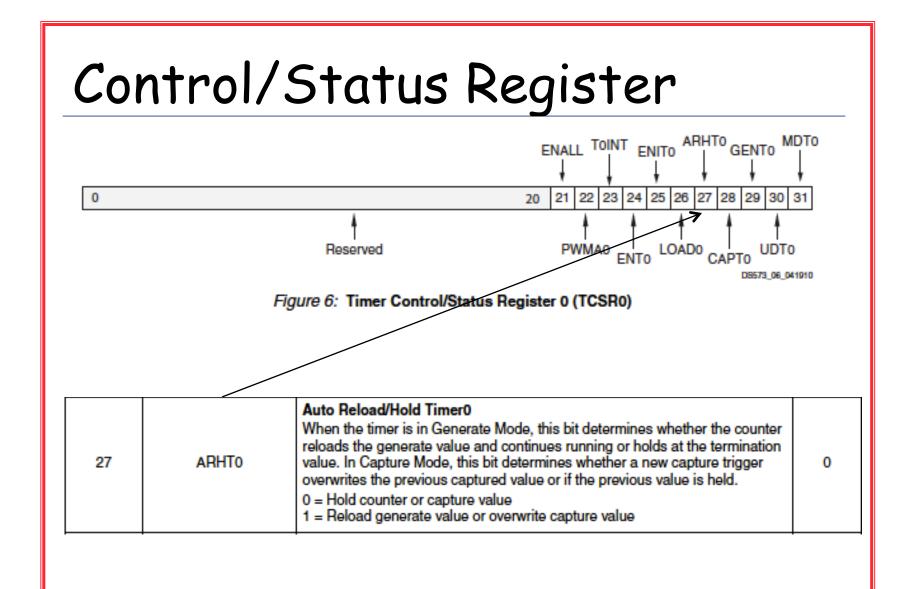

- On zero crossing, stop or automatically reload (ARHT bit)

- Generate 1 cycle interrupt (TINT bit)