Lab 1: Building A Basic SoC

Description

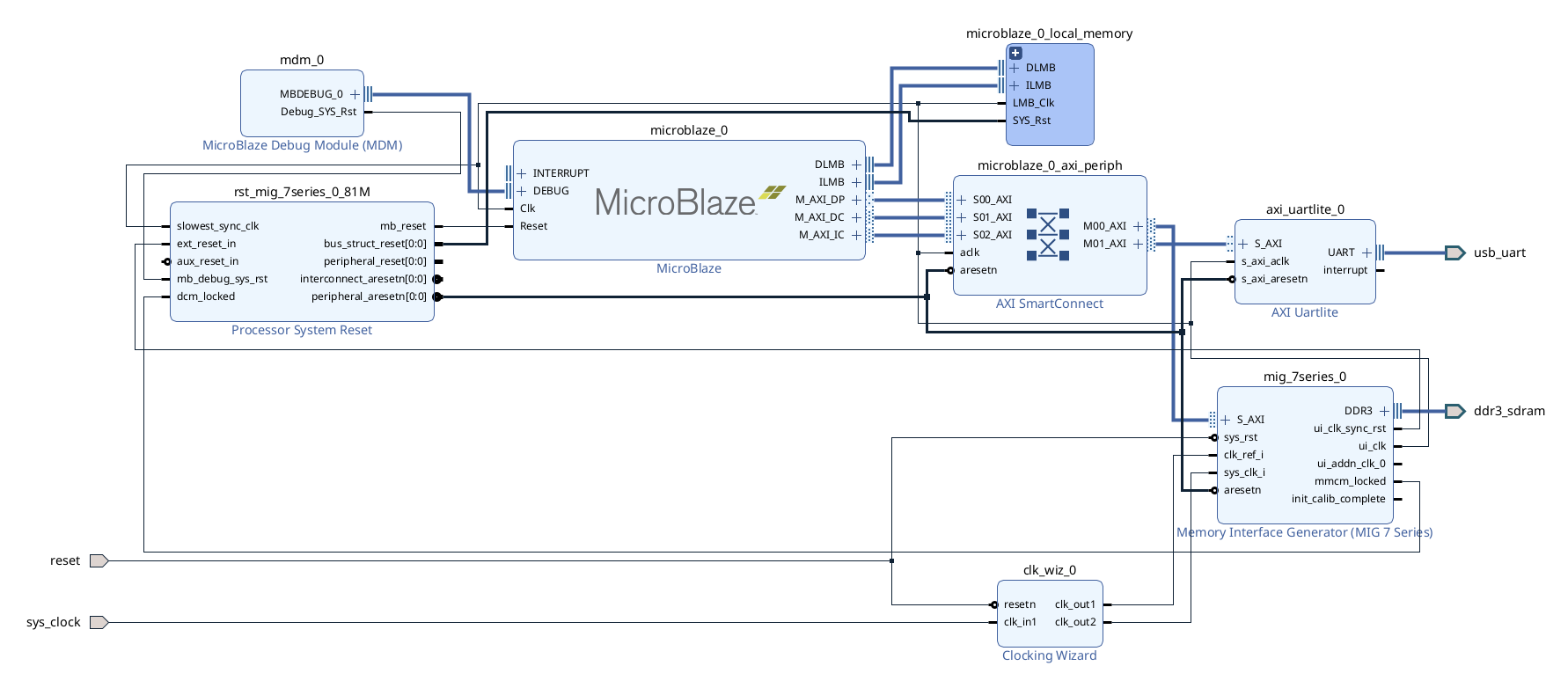

In lab 1 you will complete a provided boilerplate design of a System-on-Chip (SoC) using the AMD Vivado development suite and targeted at the Arty-A7-100 development board. Your design will contain a MicroBlaze soft processor, a USB UART serial controller, and a DDR memory controller that interfaces with components on the Arty board. The processor will be connected to the serial port and DDR memory peripherals in a shared-bus architecture. You will then program this SoC using the C programming language to print out your name and student ID five times to the screen of a desktop computer which is connected to the Arty-7 development board using the USB serial port. There will be 2 screenshot requirements for your report, so ensure you read the following instructions carefully.

Project Assignment

Use the provided base project to create a basic system-on-chip and add a UART serial controller to your SoC. Synthesize your system-on-chip, compile your software project, combine them into a bitstream, and download it onto the Arty-A7-100 development board. Create a software project and make it print out your name five times.

This may not seem like much, but at the end of this laboratory, you will have created a system-on-chip and executed a program on top of it in a bare metal environment. This represents a rudimentary but fully functional embedded system.

Directions

Preamble - Adding Arty board to Vivado:

Before opening Vivado, visit Digilent’s website and follow the instructions listed under “Install Digilent’s Board Files”. The instructions will provide you with a download link for the board files. When you extract the archive, you only need to install the “arty-a7-100” directory, other boards are not necessary for our purposes.

Vivado - Generating a bitstream

- If you have any questions, please ask for help.

- If you’re using a different version of Vivado, the steps may vary slightly. Just let me know.

- Open Vivado and create a new project.

- Give your project a name and select a location to save it. Click “Next” to continue to the “Project Type” screen.

- Select the “RTL Project” and “Do not specify sources” options and click “Next”.

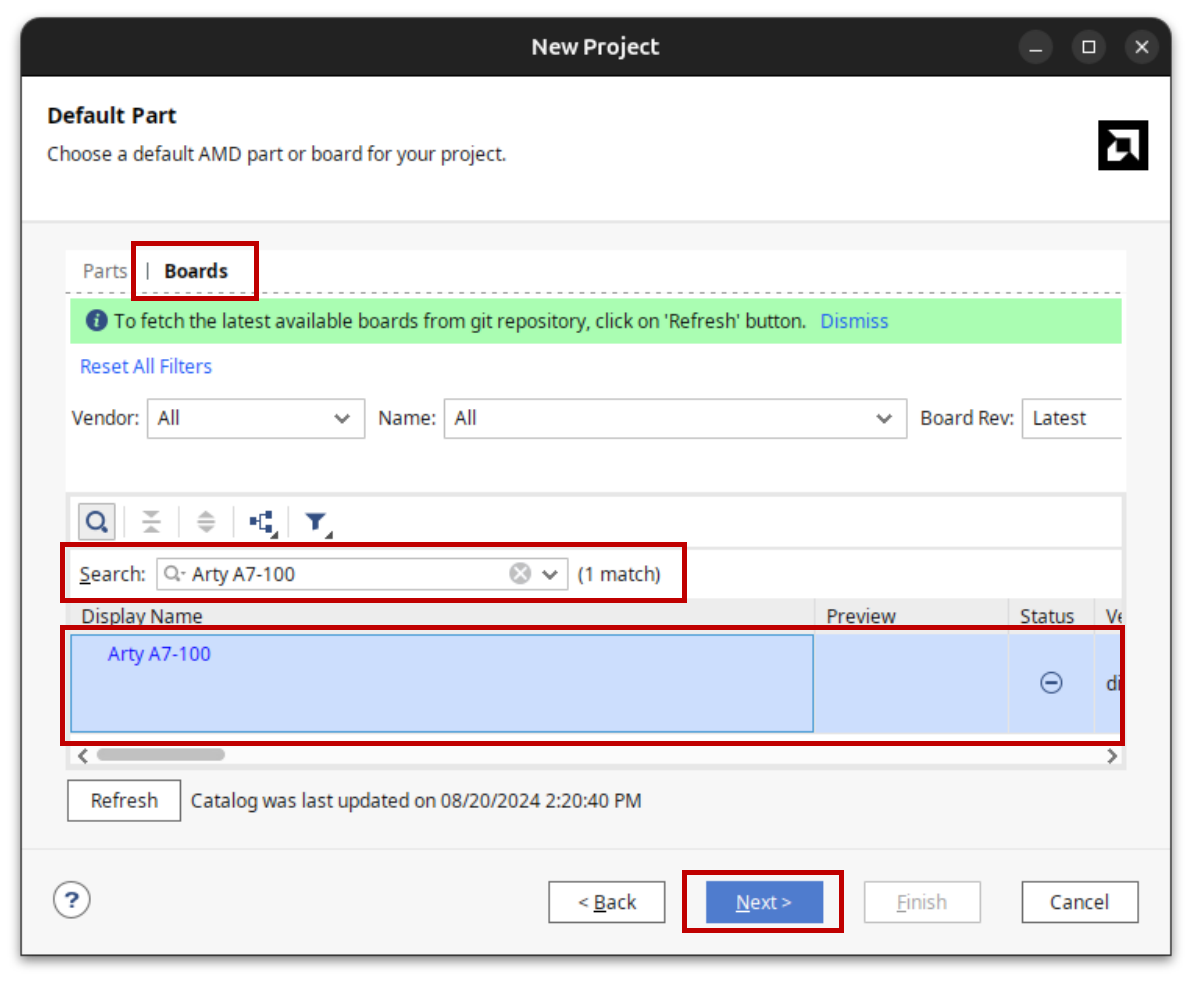

- Select the “Arty-A7-100” board and click “Next”.

- Click “Finish” to create the project.

- Create a new block design for your SoC.

- In the “Flow Navigator” panel under “IP INTEGRATOR”, click “Create Block Design”.

- Give your block design a name (e.g. “base_soc”) and click “OK”. This will open the block design window. Remember the name you give your block design, as you will need it later.

- Adding a system clock:

- In the “Diagram” panel, right-click and select “Add IP”.

- Search for “Clocking Wizard” and double-click to add it to your design.

- Double-click on the Clocking Wizard block to open the configuration window.

- In the “Board” tab, set the following parameters:

- CLK_IN1:

sys clock - RESET:

reset

- CLK_IN1:

- In the “Output Clocks” tab, set the following parameters:

- CLK_OUT1:

200 MHz - CLK_OUT2:

100 MHz - Reset Type:

Active Low - Locked:

Disable

- CLK_OUT1:

- Click “OK” to close the configuration window.

- You should see a green bar at the top of the block design window. Click on the “Run Connection Automation” option.

- Check all the boxes to automate connecting the systems clock and reset and click “OK”.

- Adding a Memory Interface Generator (MIG):

- In the “Diagram” panel, right-click anywhere in the white space and select “Add IP”.

- Search for “MIG” and double-click to add it to your design.

- Click on the “Run Block Automation” option. Make sure everything is checked in the window that pops up and click “OK”. This will automatically configure the MIG for the DDR memory on the Arty board.

- Click on the “Run Connection Automation” option.

- Set the following parameters in the “Run Connection Automation” window:

- clk_ref_i: Clock Source -

clk_wiz_0/clk_out1 (200 MHz) - sys_clk_i: Clock Source -

clk_wiz_0/clk_out2 (100 MHz) - sys_rst: Select Board Part Interface: -

reset (System Reset)

- clk_ref_i: Clock Source -

- Click “OK” to connect the MIG to the clock and reset signals.

- In the “Board” window, right-click on

Arty A7-100 > External Memory Interfaces > DDR3_SDRAMand select “Auto Connect”.

- Adding the MicroBlaze processor:

- Start by adding the MicroBlaze processor to your design.

- Search for “MicroBlaze” and add it to your design. DO NOT select the MicroBlaze V.

- Select “Run Block Automation” and set the following parameters:

- Preset:

Microcontroller - Local Memory:

32KB - Local Memory ECC:

None - Debug Module:

Debug Only - Peripheral AXI Port:

Enabled - Interrupt Controller:

Disabled - Clock Connection:

mig_7series_0/ui_clk (81 MHz)

- Preset:

- Click “OK” to finish configuring the MicroBlaze processor.

- If you still have the “Run Block Automation” option available, click on it.

- Check the

Keep Classic MicroBlazebox. This will ensure that the MicroBlaze processor is not upgraded to the RISC-V MicroBlaze V.

- Check the

- Click on the “Run Connection Automation” option.

- Change the “Master interface” to

/microblaze_0 (Periph) - Click “OK” to connect the MIG to the peripheral interface of the MicroBlaze processor.

- Change the “Master interface” to

- Adding the UART controller:

- Search for “AXI Uartlite” and add it to your design.

- Click on the “Run Connection Automation” option.

- Check the “S_AXI” box to automate connection of the UART to the MicroBlaze processor via the “AXI SmartConnect”.

- Check the “UART” box to automate connection of the UART to the USB interface.

- Click “OK” to connect the UART controller to the MicroBlaze processor and USB interface.

- Adding design constraints:

- In the “Flow Navigator” panel, click on “Add Sources”.

- Select “Add or Create Constraints” and click “Next”.

- Click “Create File” and give your constraints file a name (e.g. “base_soc.xdc”).

- Click “Finish” to create the constraints file.

In the “Sources” panel, open the constraints file

Constraints > constr_1 > base_soc.xdcand add the following constraints:## Fix clock routing conflict between "sys_clock" and "clk_wiz_0/clk_out2": ## We only have one clock (source) pin on the board, which will be ## used to route the system clock into our design. Therefore, we need ## to instruct Vivado to do the following: ## - Generate `clk_wiz_0/clk_out2` from the system clock, NOT the ## board's clock pin. ## - Route `clk_wiz_0/clk_out2` using one of the dedicated clock routes. ## ## NOTE: ## - Replace `[base_soc]_i` with the name you gave your block design ## - Verify your Clocking Wizard is indeed named "clk_wiz_0". ## - This workaround is only necessary for our particular configuration ## on the Arty-A7-100 board. set_property CLOCK_DEDICATED_ROUTE true [get_nets base_soc_i/clk_wiz_0/inst/clk_out2]

- Generate an HDL wrapper for your design:

- In the “Sources” panel, right-click on your block design

Design Sources > base_soc (base_soc.bd)and select “Create HDL Wrapper”. - Select “Let Vivado manage wrapper and auto-update”.

- Click “OK” to close the “Generate HDL Wrapper” window.

- In the “Sources” panel, right-click on your block design

- Generate the bitstream:

- In the “Flow Navigator” panel, click on “Generate Bitstream”.

- Click “OK” to generate the bitstream. Watch the progress in the top-right corner of the Vivado window.

- Once the bitstream is generated, you will be asked to “Open Implemented Design”, close this window.

- Export your project:

- Open Vivado and select

File > Export > Export Hardware. - Check the box that says “Include bitstream” and click “Finish”.

- Open Vivado and select

|

|---|

| SoC Block Design |

Vitis IDE - Creating Software Project

- To open Vitis IDE, select

Tools > Launch Vitis IDEin the top menu. - On the welcome page in Vitis, select

Create Platform Componentunder Embedded Development.- Plaform Name: E.g. “lab1_platform”

- Platform Location: In the project directory create a new folder that will be used as your project workspace. E.g.

[project directory]/labs. - Click “Next” to select a hardware design (XSA).

- Select Hardware:

- Click “Browse” and navigate to your project directory.

- Select the

base_soc_wrapper.xsafile”. - Click “Next” to select an operating system.

- Select OS Platform:

- Operating System: Select “standalone”.

- Processor: Select “microblaze_0”.

- Click “Next” to view a summary of the platform.

- Click “Finish” to create the platform. Your platform should now be visible under “Vitis Components” in the left panel.

- Now let’s create a new application to run on the platform.

- In the application menu, select

File > New Component > Application.

- In the application menu, select

- Name and Location:

- Component Name: E.g. “lab1”.

- Component Location: Select the workspace folder you created earlier.

- Click “Next” to select a target hardware.

- Select Platform:

- Platform: Select the platform you created earlier.

- Click “Next” to select an application domain.

- Select Domain:

- Name: Select “standalone_microblaze_0”.

- Click “Next” to view the application summary and finish.

- You should now see your application under “Vitis Components” in the left panel.

- Writing the Application:

- Under “Vitis Components”, find your application and navigate to

Sources > src. - Right-click on the

srcfolder and selectNew File. - Enter a file name, e.g. “lab1.c”, and click “OK”.

Use the following code snippet to get started with your application:

#include "stdio.h" #include "xil_printf.h" int main(void) { // Your code goes here: // Print your name and student ID 5 times return 0; }

- Under “Vitis Components”, find your application and navigate to

- Building and Running the Application:

- In the top menu, select

Vitis > New Feature Preview. - Select the “Serial Monitor” and click “Enable”. This will allow you to see the output of your program.

- In the top menu, select

Vitis > Serial Monitor, use baudrate9600. The serial monitor window will open in the bottom panel. - Under “Vitis Components”, select your application, then in the “Flow” panel, click “Build”.

- Once the build is complete, click “Run” to program the FPGA and run your application.

- In the top menu, select

The COM port may vary, so ensure you select the correct one. The correct COM port should be listed with the text “(FTDI)” next to it.

Submission

Submission Requirements:

Due Dates:

- Monday lab: September 1, 2025

- Wednesday lab: September 3, 2025

- Friday lab: September 5, 2025

Note:

- DO NOT paste your code in your lab report.

- DO NOT submit your entire project folder or .xsa file.

- DO NOT submit zip files or any other compressed files.

- Prepare a lab report: (Use the lab report template provided)

- Give a comprehensive account of what you did in this lab, what you learned, and anything you found interesting.

- Include the screenshots of your block design and the output of your

Vitis > Serial Monitoror Putty window. - Include only essential relevant screenshots, diagrams, and code snippets necessary to your writing in the report.

- Submit, separately, all your code files (e.g. the “helloworld.c” file).

Prelab Assignment

- What is an FPGA?

- What is a system-on-chip? Why is it different from your desktop computer system?

- What does soft-core IP mean?

- What does it mean to cross-compile a program?

- Why does it take so long to configure/build the Hardware portion of your system on the FPGA?

- How does the desktop computer program the FPGA, how does it monitor the FPGA?