Lab 1: Hello Zynq

Description

In this lab, you will learn how to build a simple System on Chip (SoC) using the Xilinx Vivado design suite. The SoC will be built around the Zynq UltraScale+ MPSoC, which is a powerful System on Chip that contains both an FPGA fabric and a quad-core ARM Cortex-A53 processor. You will learn how to create the minimum hardware design necessary to run a simple “Hello World” application on the ARM processor, and how to use the AMD Vivado and Vitis SDK.

Lab Objectives

- Create a simple Zynq Processing System (PS) design in Vivado

- Generate the necessary hardware files for software development

- Create a simple “Hello Zynq” application in Vitis SDK

- Run the application on the ARM processor

Before You Start

Before you open Vivado, you will need to install the AUP-ZU3 board files. These files contain the necessary information for Vivado to recognize the AUP-ZU3 board and its components, such as the FPGA, ARM processor, and peripherals. Without these files, you will not be able to create a hardware design for the AUP-ZU3 board in Vivado.

- Download the AUP-ZU3 board files from the following link: AUP-ZU3 Board Files

- Extract the downloaded files to a location on your computer where you can easily access them.

- Copy the extracted

board_filesfolder to the following directory:{VITIS_INSTALL_ROOT}\Vivado\2025.2\data\boards\. For example, if you installed Vivado inC:\Xilinx\Vivado\2025.2, you would copy theboard_filesfolder toC:\Xilinx\Vivado\2025.2\data\boards\.

Directions

Vivado Design

- Open Vivado and create a new project.

- Name your project e.g. “lab1” and select a location to save your project. Click “Next”.

- In the “Project Type” section, select “RTL Project”, “Do not specify sources”, and click “Next”.

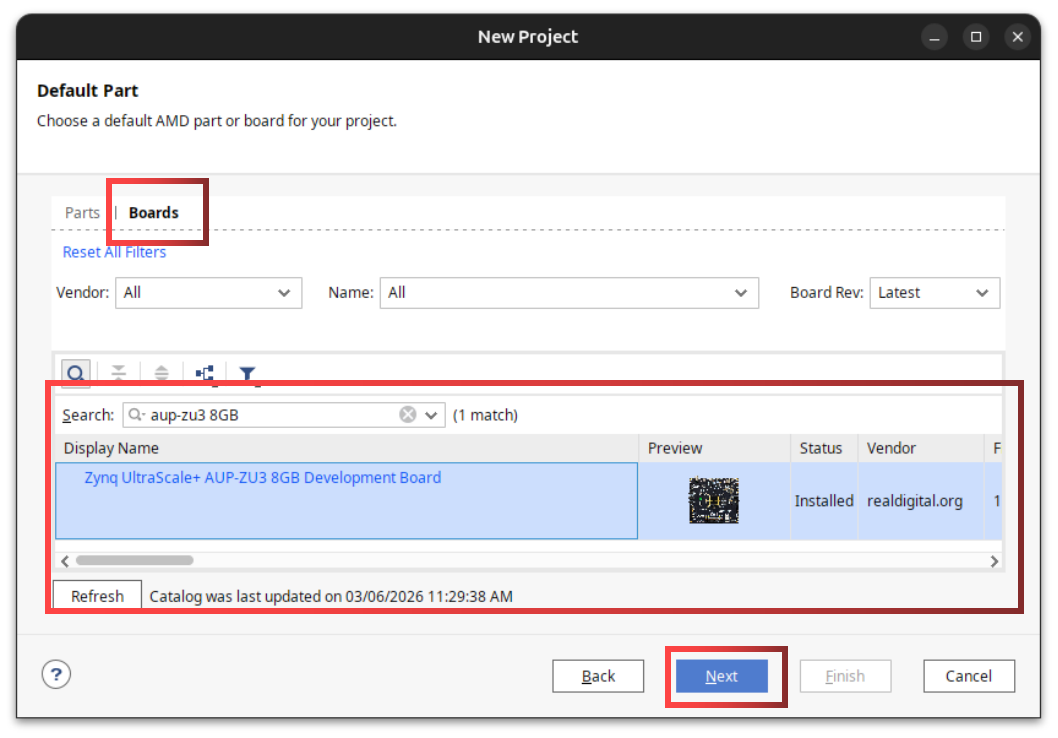

- In the “Default Part” section, select “Boards” and search for “AUP-ZU3 8GB”. Select the “AUP-ZU3” board and click “Next”, then “Finish”.

- Create a new block design.

- In the Flow Navigator, click on “Create Block Design” under the “IP Integrator” section. Name your block design e.g. “zynq_soc” and click “OK”.

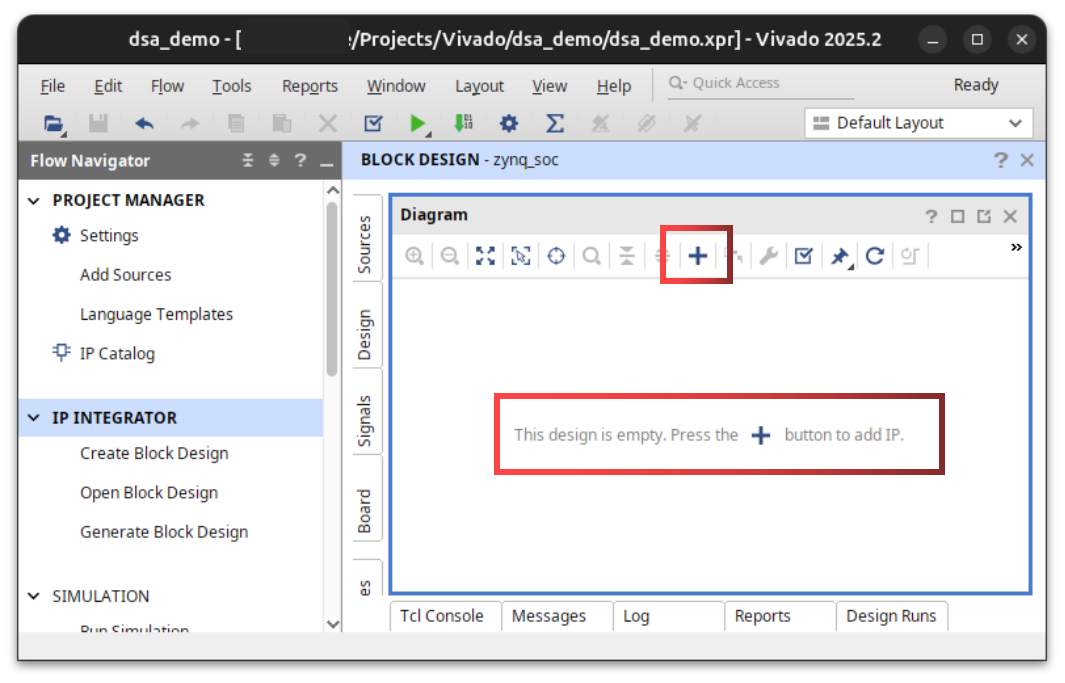

- Add the Zynq UltraScale+ MPSoC IP to your block design.

- In the block design canvas, click on “Add IP” and search for “Zynq UltraScale+ MPSoC”. Select the “Zynq UltraScale+ MPSoC” IP and click “Add IP”.

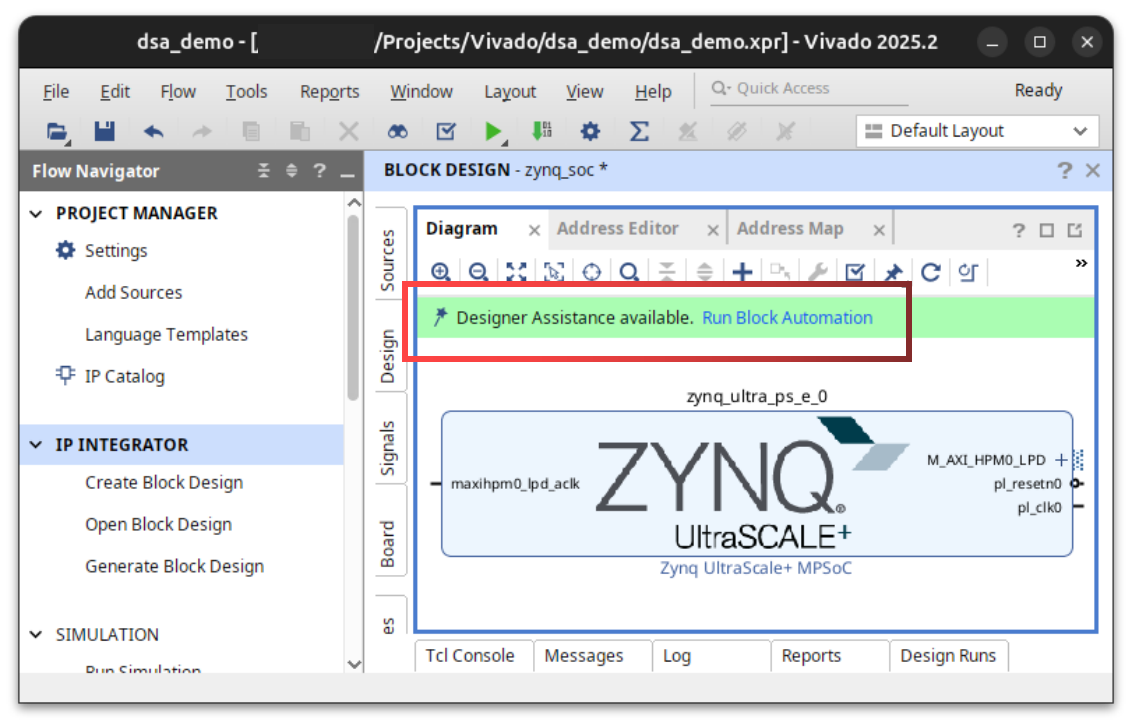

- You should now see the Zynq UltraScale+ MPSoC IP block in your block design canvas. This block represents the processing system (PS) of the Zynq SoC, which contains the ARM Cortex-A53 processor and various peripherals.

- Use the “Run Block Automation” feature to automatically configure board specific settings for the Zynq UltraScale+ MPSoC IP. Select “Apply Board Preset” and choose “AUP-ZU3-8GB”. Click “OK” to apply the preset. This will set up the necessary connections and configurations for the AUP-ZU3 board.

- In the block design canvas, click on “Add IP” and search for “Zynq UltraScale+ MPSoC”. Select the “Zynq UltraScale+ MPSoC” IP and click “Add IP”.

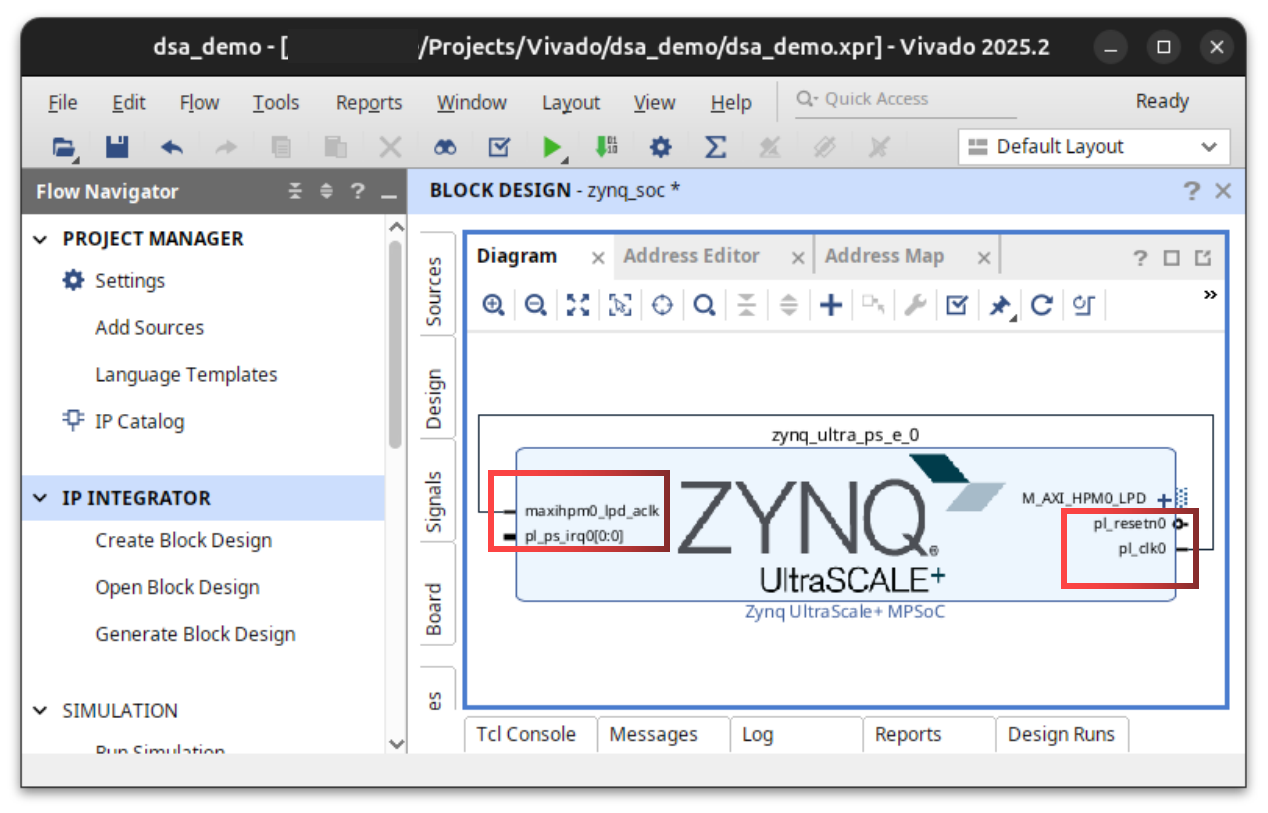

- Connecting the PL Clock

- The Zynq UltraScale+ MPSoC has a dedicated clock output that can be used to drive the programmable logic (PL) fabric. This clock is typically connected to the PL fabric through a clock wizard or directly to the PL clock input.

- In your block design, you should see a clock output from the Zynq UltraScale+ MPSoC block labeled “pl_clk0”. This is the clock output from the Zynq PS that can be used to drive the PL fabric logic. We’ll use this clock in future labs to drive the logic in the PL fabric.

- For now, use your mouse to click and drag from the “pl_clk0” output pin (right side) on the Zynq UltraScale+ MPSoC block to the “maxihpm0_lpd_aclk” input pin (left) on the Zynq UltraScale+ MPSoC block. This will create a connection between the PS clock output and the PL clock input. This connection is necessary for the PS to be able to drive logic in AXI interfaces between the PS and PL.

- Validate your block design.

- Click on the “Validate Design” button (checkmark icon) to check for any errors in your block design. If there are any errors, Vivado will provide feedback on what needs to be fixed. Make sure to resolve any errors before proceeding.

- Generate an HDL wrapper for your block design.

- In the “Sources” panel, right-click on your block design

Design Sources > zynq_soc (zynq_soc.bd)and select “Create HDL Wrapper”. - Select “Let Vivado manage wrapper and auto-update”.

- Click “OK” to close the “Generate HDL Wrapper” window.

- In the “Sources” panel, right-click on your block design

- Generate the bitstream:

- In the “Flow Navigator” panel, click on “Generate Bitstream”.

- Click “OK” to generate the bitstream. Watch the progress in the top-right corner of the Vivado window.

- Once the bitstream is generated, you will be asked to “Open Implemented Design”, close this window.

- Export your project:

- Open Vivado and select

File > Export > Export Hardware. - Check the box that says “Include bitstream” and click “Finish”.

- Open Vivado and select

Vitis SDK

- Create a workspace for your Vitis SDK project.

- On your computer, create a new folder to serve as your workspace for Vitis SDK projects. For example, you could create a folder called “labs” in your project directory.

- Open Vitis SDK and create a new platform component.

- On the welcome page in Vitis, select

New Platform Componentunder Embedded Development. - Plaform Name: E.g. “lab1bsp”. _NB: “_bsp” stands for “Board Support Package”, this is a common naming convention for platform projects in Vitis SDK.

- Platform Location: Select the workspace folder you created earlier. E.g.

[project directory]/labs. - Click “Next” to select a hardware design (XSA).

- Select Hardware:

- Click “Browse” and navigate to your project directory.

- Select the

zynq_soc_wrapper.xsafile”. This file is generated by Vivado when you export your hardware design, and it contains all the necessary information about the hardware design for Vitis SDK to create a platform. Yours may be named differently depending on the name of your block design, but it should be in the same directory as your Vivado project and have a.xsaextension. - Click “Next” to select an operating system.

- Select OS Platform:

- Operating System: Select “standalone”. This means we will be running a simple application without an operating system, directly on the hardware.

- Processor: Select “psu_cortexa53_0”. This is the ARM Cortex-A53 processor in the Zynq PS that we will be using to run our application.

- Architecture: 64-bit.

- Click “Next” to view a summary of the platform.

- Click “Finish” to create the platform. Your platform should now be visible under “Vitis Components” in the left panel.

- Wait for Vitis SDK to finish creating the platform. This may take a few minutes as it processes the hardware design and generates the device tree, peripheral drivers, and board configurations.

- On the welcome page in Vitis, select

- Create a new application project.

- In the application menu, select

File > New Component > Application. - Component Name: E.g. “lab1”.

- Component Location: Select the workspace folder you created earlier.

- Click “Next” to select a target hardware.

- Select Platform:

- Platform: Select the platform you created earlier (e.g. “lab1_bsp (aup-zu3-8gb)”).

- Click “Next” to select an application domain.

- Select Domain:

- Name: Select “standalone_psu_cortexa53_0”. This domain corresponds to the standalone operating system running on the ARM Cortex-A53 processor in the Zynq PS. In our case, “standalone” means we will be running a simple application without an operating system, directly on the hardware, “bare metal”.

- Click “Next” to view the application summary and finish.

- You should now see your application under “Vitis Components” in the left panel.

- Wait for Vitis SDK to finish creating the application. This may take a few minutes as it sets up the project structure and generates necessary files.

- In the application menu, select

- Writing the Application:

- Under “Vitis Components”, find your application and navigate to

Sources > src. - Right-click on the

srcfolder and selectNew File. - Enter a file name, e.g. “lab1.cpp”, and click “OK”. NB: You can use either C or C++ for your application, the file extension you use will determine the compiler used on your project (.c for C, .cpp for C++).

- Use the following code snippet to get started with your application:

#include <iostream> int main(void) { // Print "Hello Zynq!" to the console. return 0; }

- Under “Vitis Components”, find your application and navigate to

- Building and Running the Application:

- In the top menu, select

Vitis > Serial Monitor, use baudrate115200. The serial monitor window will open in the bottom panel. - Under “Vitis Components”, select your application, then in the “Flow” panel, click “Build”.

- Once the build is complete, click “Run” to program the FPGA and run your application.

- If everything is set up correctly, you should see “Hello Zynq!” printed in the serial monitor.

- In the top menu, select

Congratulations!

You’ve successfully built and run your first application on the Zynq SoC! In future labs, we will build more complex hardware designs and applications, but this is the foundation for everything we will do in this course.

Next Steps

In the next lab, we will implement an example compute intensive application on the ARM processor and CPU optimization techniques, and benchmarking the performance of our application.

Troubleshooting

If you encounter any issues during this lab, here are some common troubleshooting steps:

- If your platform is not available in Vitis after you created it, you may have to delete your workspace and start over. My Vitis has been glitching on new workspaces.

- If you are having trouble with the serial monitor, make sure you have the correct COM port selected and that your baudrate is set to 115200.